# AnDAPT Current-Mode Two-Phase DrMOS Controller

# Power Component: C870\_B

## **Product Description**

The C870 B Power Component is a customizable, two-phase, current-mode DrMOS controller designed for point-of-load (POL) applications. Combine with other Power Components to create a custom-defined, AnDAPT AmP on-demand PMIC. Power Components are software components, accessible through the WebAmP<sup>TM</sup> cloud-based development tool, allowing users to create their own PMIC. The C870 B has been developed to interface with industry-standard DrMOS devices such as Vishay SiC645A or Intersil/Renesas ISL99227 with 3.3V compatible tri-state PWM input. The DrMOS is a fully integrated power stage that integrates high and low side MOSFETs and a high-performance driver with integrated bootstrap diode. Maximum output current is based on selected external DrMOS and on thermal design of specific application.

#### **Features**

- Constant frequency, emulated peak current mode, twophase DrMOS controller with built-in slope compensation

- Adjustable output voltage with down to 2.5 mV resolution

- 1% voltage accuracy

- Efficiency up to 94%

- Adjustable switching clock 500-1000 kHz (each phase switches at half of the clock frequency)

- Adjustable bandwidth, gain & phase margin

- Adjustable protections: Input Undervoltage Lockout (ViUVLO), Output Undervoltage Lockout (VoUVLO), Cycle-by-cycle Overcurrent Protection (OCP), Output Overvoltage Protection (OVP)

- Power-good flag output and Enable input

- Component included in the WebAmP<sup>™</sup> development tool

## **Applications**

- FPGA/SoC, processor power management

- Telecom servers, networking equipment

- Industrial equipment and medical systems

Figure 1. C870 B Power Component

| >VINFB   |                      | PWM0>  |

|----------|----------------------|--------|

| >EN      |                      | PWM1>  |

| >VFB     |                      | CFP>   |

| >ISENSE0 | C870 (B_1_0)         | PGood> |

| >ISENSE1 | PWM Multiphase DrMOS | OVP>   |

| >PSFLT   | TP_DrMOS1            | OCP>   |

| >IREF0   |                      | OTP>   |

| >IREF1   |                      | UVLO>  |

| >TSENSE  |                      | DCM>   |

#### **Product Details**

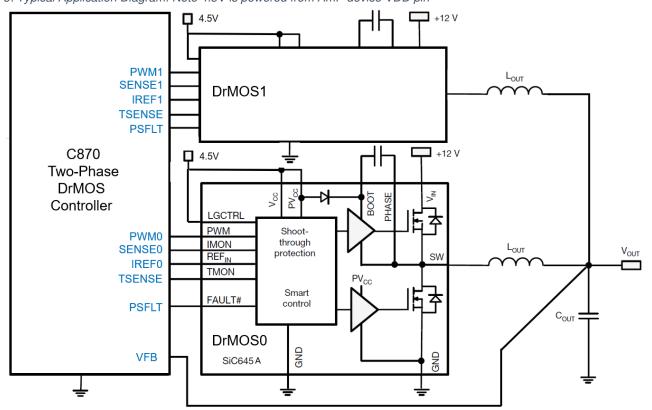

The C870 B 2-phase Synchronous Buck DrMOS controller power component symbol is shown in Figure 1. The controller drives two DrMOS integrated power stages 180° out-of-phase with connections as shown in Figure 2 and described in the Pin Function and Description Table. A typical application diagram is shown in Figure 3. Output voltage feedback is fed back into a high-performance voltage error digitizer that provides tight voltage regulation accuracy even under transient conditions. The digital compensator's PID gain parameters are user adjustable. The switching frequency is user-selectable with the option to sync to an external clock connected to a GPIO pin.

The output voltage and maximum current are specified by the power engineer during customization using AnDAPT's cloud based WebAmp development software. The C870 B component has customizable control and status pins including an enable input, an optional power-good output, and optional output flags to signal when the system senses an overvoltage (OVP), overcurrent (OCP), undervoltage lockout (UVLO), catastrophic DrMOS failure (CFP) or overtemperature (OTP) condition. The threshold values are configured in the WebAmp tool.

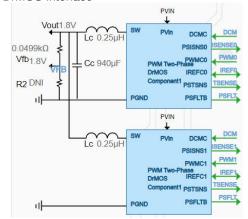

Figure 2: DrMOS Interface

Soft-start and soft-stop ramp times are also specified using the WebAmp tool. Additional sequencing options are available when used in conjunction with the C420 Sequencer, by interconnecting signals EN and PGOOD to provide customizable dependencies and customizable delays between each sequence step.

# Pin Function and Description Table

| Port<br>Name       | SiC645<br>Name | I/O | Description                                                                                                                                                                                                                                                              |  |

|--------------------|----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| OVP                |                | 0   | Over-Voltage Protection fault flag that can be routed to internal logic and/or a GPIO                                                                                                                                                                                    |  |

| OCP                |                | 0   | Over-Current Protection fault flag that can be routed to internal logic and/or a GPIO                                                                                                                                                                                    |  |

| OTP                |                | 0   | DrMOS Over-Temperature Protection fault flag that can be routed to additional internal logic and/or a GPIO pin                                                                                                                                                           |  |

| UVLO               |                | 0   | Output Under-Voltage Lock-Out fault flag that can be routed to internal logic and/or a GPIO                                                                                                                                                                              |  |

| PGood              |                | 0   | Controller Power Good signal                                                                                                                                                                                                                                             |  |

| CFP                |                | 0   | Catastrophic Fault Protection fault flag that can be routed to internal logic and/or a GPIO                                                                                                                                                                              |  |

| VINFB              |                | I   | Input voltage (PVIN) measurement for ViUVLO protection                                                                                                                                                                                                                   |  |

| TSENSE             | TMON           | I   | Analog temperature signal from DrMOS Power Stage to C870_B controller                                                                                                                                                                                                    |  |

| PSFLT              | FAULT#         | I   | Open-drain fault signal from DrMOS Power Stage to C870_B controller                                                                                                                                                                                                      |  |

| ISENSE0<br>ISENSE1 | IMON           | I   | Analog current monitor signal from DrMOS Power Stage to C870_B controller. In the PCB, these signals should be routed as a sensitive differential pair with their respective IREF signals.                                                                               |  |

| IREF0<br>IREF1     | REFIN          | I   | Reference voltage for DrMOS IMON signal and C870_B ISENSE differential input amplifiers. Route these as differential pairs with their respective ISENSE lines from the AmP device to the DrMOS. Run a separate trace from the AmP device 1.2V VCC pin to the DrMOS pins. |  |

| DCM                | LGCTRL         | 0   | Reserved for future DCM (discontinuous mode) control. In Webamp leave the DCM signal unconnected, and in the PCB, connect LGCTRL to the DrMOS VCC pin.                                                                                                                   |  |

| EN                 |                | I   | Enable DrMOS controller                                                                                                                                                                                                                                                  |  |

| PWM0<br>PWM1       | PWM            | 0   | DrMOS power stage gate driver control signal output from DrMOS controller                                                                                                                                                                                                |  |

| VFB                |                | I   | VOUT feedback for DrMOS controller                                                                                                                                                                                                                                       |  |

Figure 3: Typical Application Diagram. Note 4.5V is powered from AmP device VDD pin