# AnDAPT DrMOS Controller Buck, LDO & LDSW PMIC

# Adaptable PMIC AnD7122

## **Product Description**

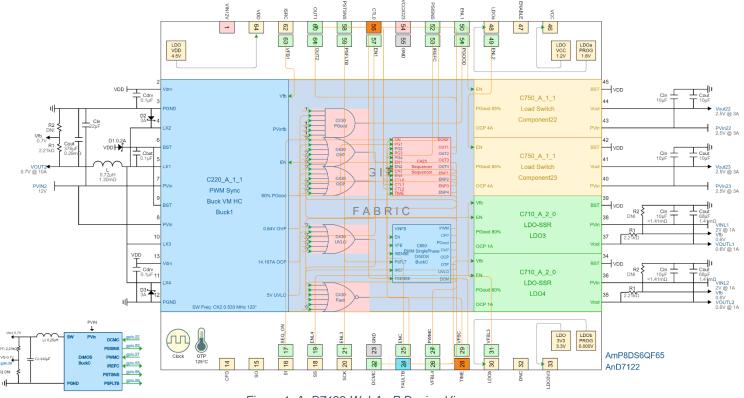

The AnD7122 Adaptable PMIC uses AnDAPT AmP<sup>™</sup> advanced technology consisting of fully flexible digital fabric embedded with high performance analog blocks. The AnD7122 consists of one configurable DrMOS controller, one 10A high current synchronous Buck regulator, two high current LDOs, two high current Load Switches, along with an integrated sequencer and four additional auxiliary LDOs. The AnD7122 is fully tested and ready for use in designs. The AnD7122 Buck regulators use voltage-mode control. The user can modify output voltages and rail sequencing using external resistors or WebAdapter<sup>™</sup> online tool. The sequencer can be programmed based on either timed delays or Power Good (PGOOD) signals. Adaptable PMICs provide fastest prototyping and time-to-market, while providing best-in-class performance and flexibility. The Adaptable PMIC is optimized to power high-end processors by integrating multiple power rails into single-chip designs.

#### **Features**

- One 40 A (thermally limited) DrMOS Controller  $V_{\text{OUT}}$ : 0.7 V to 5 V

- One 10 A Buck,  $\mathsf{PV}_{\mathsf{IN}}$  4.75 V to 14 V,  $\mathsf{V}_{\mathsf{OUT}}\!\!:$  0.7 V to 5.0 V

- Two 1 A LDOs.  $V_{\text{OUT}}$ : 0.6 V to 3.3 V

- Two 6 A Load Switches. Vout: 0.6 V to 5 V

- Protections. Input output UVLO, OCP, OVP, OTP

- Four 200 mA aux. LDOs. Vout: 1.2 V, 1.8 V, 2.5 V, 3.3 V

- Adjustable output voltage with 2.4 mV resolution

- 1% load regulation

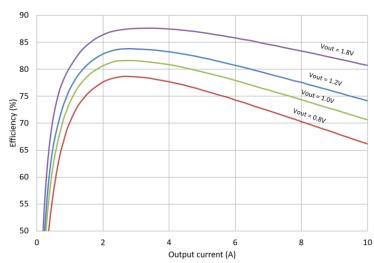

- Buck regulator efficiency up to 95%

- PGOOD flag output and Enable input

- Soft start/stop, sequencing, pre-bias startup

- -40°C to +125°C operating junction temperature

- Easy WebAmP upgrade path to On-Demand PMIC

## **Applications**

- On-demand power management, multi-rail power integration

- Powering server, processor, memory, storage, network switcher and router platforms

- Powering FPGA, processor, SSD, subsystem power control & sequencing

#### **Product Detail**

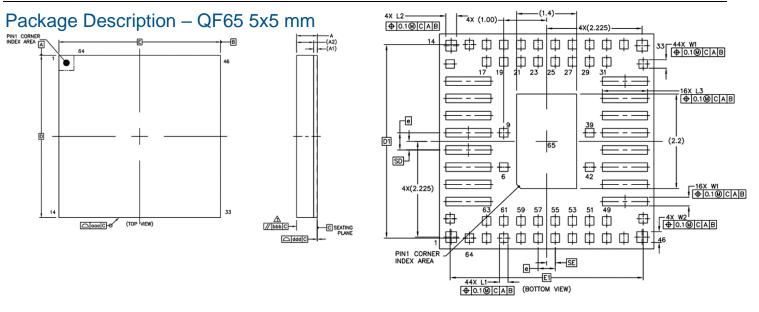

The AnD7122 adaptable PMIC consists of one customizable DrMOS Controller, one 10A, two high current LDOs, two high current Load Switches and status pins including enable input and an optional PGOOD output. Evaluation Board support includes the AnD7122EB. DrMOS device support includes: SiC645A Vishay Siliconix and ISL99227 Intersil Renesas. The AnD7122 is available in a 5mm x 5mm thermally enhanced QFN package.

Figure 1. AnD7122 WebAmP Design View

#### **Order Information**

| Part Number | Package | Description                        | Availability |  |  |  |

|-------------|---------|------------------------------------|--------------|--|--|--|

| AnD7122QF65 | QF65    | DrMOS Cntrl, Buck, LDO & LDSW PMIC | Now          |  |  |  |

#### Package Marking Example – QF65

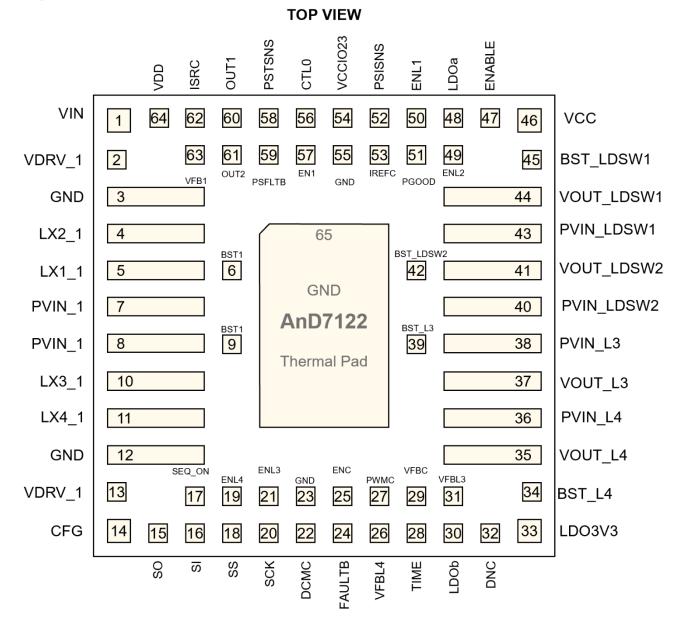

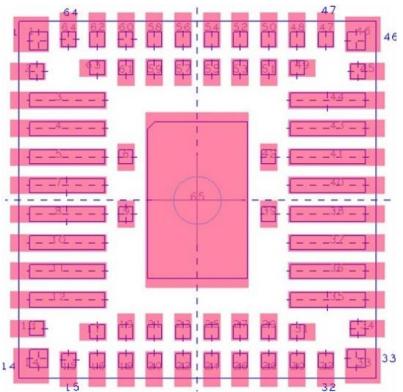

## Package Pinout

Figure 2. AnD7122 package pinout

# Pin Function and Description

| Pin Name | Pin # | Description                                                                                                                               |

|----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------|

| VIN      | 1     | VIN bias supply for: VDD, VCC, LDO3V3, LDO1V8, LDO2V5                                                                                     |

| VDRV_1   | 2     | Low side MOSFET gate drive supply for High Current Sync Buck 1                                                                            |

| GND      | 3     | Low side MOSFET source for Buck 1, must be connected to GND                                                                               |

| LX2_1    | 4     | Switch node (LX) Low side MOSFET drain for High Current Sync Buck 1                                                                       |

| LX1_1    | 5     | Switch node (LX) High side MOSFET source for High Current Sync Buck 1                                                                     |

| BST1_1   | 6     | Bootstrap pin High side MOSFET gate drive for High Current Sync Buck 1                                                                    |

| PVIN_1   | 7     | Power Input for High Current Sync Buck 1                                                                                                  |

| PVIN_1   | 8     | Power Input for High Current Sync Buck 1                                                                                                  |

| BST2_1   | 9     | Bootstrap pin High side MOSFET gate drive for High Current Sync Buck 1                                                                    |

| LX3_1    | 10    | Switch node (LX) High side MOSFET source for High Current Sync Buck 1                                                                     |

| LX4_1    | 11    | Switch node (LX) Low side MOSFET drain for High Current Sync Buck 1                                                                       |

| GND      | 12    | Low side MOSFET source for Buck1, must be connected to GND                                                                                |

| VDRV_1   | 13    | Low side MOSFET gate drive supply for High Current Sync Buck1                                                                             |

| CFG      | 14    | CFG input active high configuration restart. Device is held in reset while signal is high. Reconfiguration is triggered on negative edge. |

| SO       | 15    | SPI SO output transmits SPI commands during configuration                                                                                 |

| SI       | 16    | SPI SI input receives SPI data during configuration                                                                                       |

| SEQ_ON   | 17    | Enable Sequencer                                                                                                                          |

| SS       | 18    | SPI SS output slave, select when master, input when slave during configuration                                                            |

| ENL4     | 19    | Enable LDO4                                                                                                                               |

| SCK      | 20    | SPI SCK output clock when master, input clock when slave during configuration                                                             |

| ENL3     | 21    | Enable LDO3                                                                                                                               |

| DCMC     | 22    | DrMOS lower gate control signal output for Discontinuous current mode                                                                     |

| GND      | 23    | Ground                                                                                                                                    |

| FAULTB   | 24    | Fault output open drain active low. Dual function pin, shared with DONE output, signals end of configuration when high-Z                  |

| ENC      | 25    | Enable DrMOS                                                                                                                              |

| VFBL4    | 26    | Feedback voltage for LDO4                                                                                                                 |

| PWMC     | 27    | PWM output for DrMOS power stage                                                                                                          |

| TIME     | 28    | Sequencer mode control, high = TIME mode, low = PGood mode                                                                                |

| VFBC     | 29    | Feedback voltage for DrMOS                                                                                                                |

| LDOb     | 30    | LDO 2.5V output                                                                                                                           |

| VFBL3    | 31    | Feedback voltage for LDO3                                                                                                                 |

| DNC      | 32    | Do not connect, floating                                                                                                                  |

Table 1. AnD7122 pinout

# Pin Function and Description (continued)

| Pin Name   | Pin # | Description                                                                             |

|------------|-------|-----------------------------------------------------------------------------------------|

| LDO3V3     | 33    | LDO output 3.3V                                                                         |

| BST_L4     | 34    | LDO 4 MOSFET bias driver                                                                |

| VOUT_L4    | 35    | LDO 4 MOSFET source output                                                              |

| PVIN_L4    | 36    | LDO 4 MOSFET drain power input                                                          |

| VOUT_L3    | 37    | LDO 3 MOSFET source output                                                              |

| PVIN_L3    | 38    | LDO 3 MOSFET drain power input                                                          |

| BST_L3     | 39    | LDO 3 MOSFET bias driver                                                                |

| PVIN_LDSW2 | 40    | LDSW 2 MOSFET drain power input                                                         |

| VOUT_LDSW2 | 41    | LDSW 2 MOSFET source output                                                             |

| BST_LDSW2  | 42    | LDSW 2 MOSFET bias driver                                                               |

| PVIN_LDSW1 | 43    | LDSW 1 MOSFET drain power input                                                         |

| VOUT_LDSW1 | 44    | LDSW 1 MOSFET source output                                                             |

| BST_LDSW1  | 45    | LDSW 1 MOSFET bias driver                                                               |

| VCC        | 46    | VCC, LDO 1.2V output and input for digital circuitry                                    |

| ENABLE     | 47    | Chip enable, AnD7122 powered on when floating (default), powered down when pulled low.  |

| LDOa       | 48    | LDO 1.8V adjustable output                                                              |

| ENL2       | 49    | Enable Load Switch 2                                                                    |

| ENL1       | 50    | Enable Load Switch 1                                                                    |

| PGOOD      | 51    | Global Power Good, includes Buck1, High Current Sync Buck 2 and DrMOS                   |

| PSISNS     | 52    | Current monitor input from DrMOS Power Stage to controller                              |

| IREFC      | 53    | DrMOS power stage REFIN signal                                                          |

| VCCIO23    | 54    | Supply input to GPIO bank, 3.3V                                                         |

| GND        | 55    | Digital ground                                                                          |

| CTL0       | 56    | Sequencer Control 0                                                                     |

| EN1        | 57    | Enable High Current Sync Buck 1                                                         |

| PSTSNS     | 58    | Temperature monitor input from DrMOS Power Stage to controller                          |

| PSFLTB     | 59    | Open drain fault input pin from DrMOS Power Stage to controller.                        |

| OUT1       | 60    | Sequencer OUT1 Connect to Buck 1 EN pin to be the first in sequence.                    |

| OUT2       | 61    | Sequencer OUT2 Connect to High Current Sync Buck 2 EN pin to be the second in sequence. |

| ISRC       | 62    | NC (No connect)                                                                         |

| VFB2       | 63    | Feedback for High Current Sync Buck 2                                                   |

| VDD        | 64    | VDD LDO 4.5V output, input bias for analog circuitry                                    |

| GND        | 65    | Thermal pad, connect to GND                                                             |

## Absolute Maximum Ratings

over operating free-air temperature range

|                                     |                                             | Min | Max | Unit |

|-------------------------------------|---------------------------------------------|-----|-----|------|

| Drain to Source Voltage             |                                             | -1  | 22  | V    |

| V <sub>IN</sub> Bias Supply         |                                             | -1  | 22  | V    |

| Boost Voltage, referenced to Source |                                             | -1  | 6.6 | V    |

| All other pins                      |                                             | -1  | 6.6 | V    |

| Continuous Drain Current            | Package power dissipation may limit current |     | 8   | А    |

| Temperature range                   | Operating Junction temperature range, TJ    | -40 | 125 | °C   |

|                                     | Storage temperature range, Tstg             | -65 | 150 | Ŭ    |

## **ESD** Ratings

|                         |                      | Value | Unit |

|-------------------------|----------------------|-------|------|

| Electrostatio Discharge | Human body model     | ±2000 | V    |

| Electrostatic Discharge | Charged device model | ±500  | V    |

### **Thermal Information**

| Symbol                                         | Thermal Metric                                                     | QF65              | Unit |  |  |  |

|------------------------------------------------|--------------------------------------------------------------------|-------------------|------|--|--|--|

| $\theta_{JA(effective)}$                       | Effective Junction-to-ambient thermal resistance (System Level)*   | 20                | °C/W |  |  |  |

| Package Manufacturer ratings (JEDEC reference) |                                                                    |                   |      |  |  |  |

| θις                                            | Junction-to-case (top) thermal resistance                          | 11                | °C/W |  |  |  |

| θ <sub>JB</sub>                                | Junction-to-board thermal resistance                               | 9                 | °C/W |  |  |  |

| *0                                             | assured on AnDART AnDR240ER Evaluation Roard and AmP2DR1REV/5.0 Do | monstration Board |      |  |  |  |

$^{*}\theta_{JA\{effective\}}$  measured on AnDAPT AnD8240EB Evaluation Board and AmP8DB1REV5.0 Demonstration Board

## Package Dissipation Ratings

| Package | ΘJA(effective) | T <sub>A</sub> = 55°C<br>Power Rating (W)<br>Still air flow | T <sub>A</sub> = 55°C<br>Power Rating (W)<br>200 LFM air flow | T <sub>A</sub> = 55°C<br>Power Rating (W)<br>400 LFM air flow |

|---------|----------------|-------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------|

| QF65    | 20             | 3.5                                                         | 3.8                                                           | 4.1                                                           |

## **Recommended Operating Conditions**

over operating free-air temperature range

|                                         | Min  | Max  | Unit |

|-----------------------------------------|------|------|------|

| PVIN_1                                  | 4.75 | 14   | V    |

| LX1_1, LX2_1, LX3_1, LX4_1              | -0.8 | 14   | V    |

| BST1 to LX1_1, LX2_1, LX3_1, LX4_1 pins | -0.1 | 5.5  | V    |

| VDRV_1                                  | 3.0  | 5.5  | V    |

| VCCIO23                                 | 3.14 | 3.46 | V    |

| All other pins                          | -0.3 | 3.66 | V    |

| TA                                      | -40  | 85   | С°   |

| TJ                                      | -40  | 125  | °C   |

## **Digital GPIO Electrical Characteristics**

V<sub>IN</sub>=12V and T<sub>A</sub>=25°C

| I/O      | ١    | /ccio (V | ´)   | VIL (V) |     | Vін (V) |              | Vol (V) Voh (V) |             | Iol  | Іон  |

|----------|------|----------|------|---------|-----|---------|--------------|-----------------|-------------|------|------|

| Standard | Min  | Тур      | Max  | Min     | Max | Min     | Max          | Max             | Min         | (mA) | (mA) |

| 3.3 V    | 3.14 | 3.3      | 3.46 | -0.3    | 0.8 | 2.0     | Vccio + 0.24 | 0.4             | Vccio – 0.5 | 2    | -2   |

## **DrMOS** Features

- PWM, voltage-mode DrMOS controller

- Output voltage resolution 2.4 mV

- 1% voltage accuracy

- Efficiency up to 94%

- Switching frequency 533 kHz

- Protections: Input Undervoltage Lockout (ViUVLO), Output Undervoltage Lockout (VoUVLO), Overcurrent Protection (OCP), Overvoltage Protection (OVP), Over temperature Protection (OTP), Short-circuit Protection (SCP)

- Power-good flag output and Enable input

- Controller junction temperature range -40°C to +125°C

- Component included in the WebAmP<sup>™</sup> development tool

#### **Applications**

- On-demand power management, multi-rail power integration

- Powering server, processor, memory, storage, network switcher and router platforms

- FPGA, processor, SSD, subsystem power control & sequencing

| >VINFB  |                         | PWM>   |

|---------|-------------------------|--------|

| >EN     |                         | CFP>   |

| >VFB    |                         | PGood> |

| >ISENSE | C860<br>PWM SinglePhase | OVP>   |

|         | DrMOS<br>BuckC          | OCP>   |

| >PSFLT  |                         | OTP>   |

| >IREF   |                         | UVLO>  |

| >TSENSE |                         | DCM>   |

Figure 3. C860 Power Component

# DrMOS Product Detail

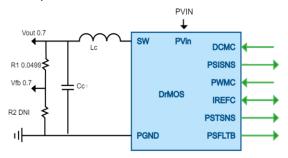

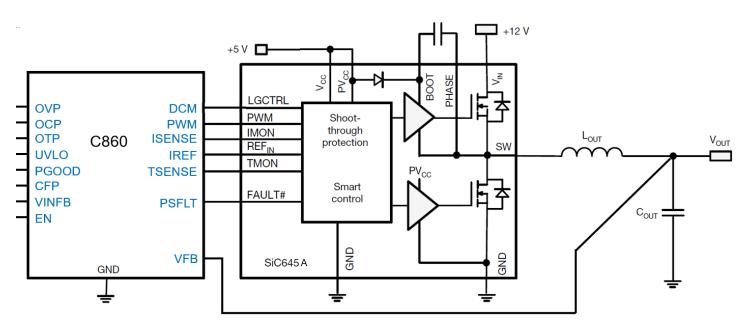

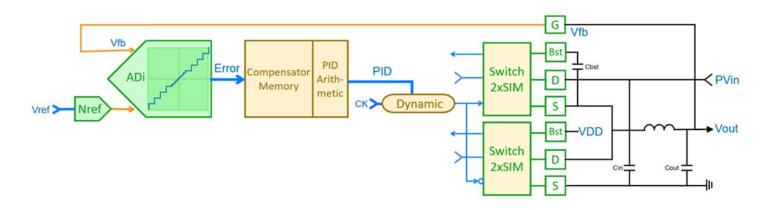

The C860 Synchronous Buck controller power component symbol is shown in Figure 3. The controller drives a DrMOS integrated power stage with connections as shown in Figure 4 and described in the Pin Function and Description Table 2. A typical application diagram is shown in Figure 5.

Output voltage feedback is compared against an internal reference using a high-performance voltage-error digitizer that provides tight voltage regulation accuracy. Pulse-width modulated (PWM), voltage-mode regulation is implemented with PID compensation. The switching frequency is either generated internally via an oscillator with selectable frequencies or provided via an external pin.

The customizable output voltage is specified during customization using AnDAPT's cloud-based WebAmp development software. The C860 component has customizable control and status pins including enable input, an optional power-good output, and optional output flags to signal when the system triggers an overvoltage (OVP), overcurrent (OCP), undervoltage lockout (UVLO), catastrophic DrMOS failure (CFP) or over temperature (OTP) condition. The threshold values are specified using the WebAmp tool. See C860 datasheet for more DrMOS details.

Customizable soft-start and soft-stop slew rates are set using the WebAmp tool. Additional sequencing options are available when used in conjunction with the C420 Sequencer, by interconnecting signals EN and PGood to provide customizable dependencies and customizable delays between each sequence step. See C420 datasheet for more sequencer details.

Figure 4. AnD7122 interface with DrMOS

# **DrMOS** Compatible Devices

Compatible devices include:

SiC645A Vishay Siliconix

ISL99227 Intersil Renesas

### Pin Function and Description Table

| Port Name | GPIO<br>Name | SiC645<br>pin Name | I/O | Description                                                                                                                                                                    |

|-----------|--------------|--------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OVP       |              |                    | 0   | Over Voltage Protection fault flag for internal connection to AmP fault manager                                                                                                |

| OCP       |              |                    | 0   | Over Current Protection fault flag for internal connection to AmP fault manager                                                                                                |

| OTP       |              |                    | 0   | Over Temperature Protection fault flag for internal connection to AmP fault manager                                                                                            |

| UVLO      |              |                    | 0   | Input Under Voltage Lock Out fault flag for internal connection to AmP fault manager                                                                                           |

| PGOOD     |              |                    | 0   | Controller Power Good signal                                                                                                                                                   |

| CFP       |              |                    | 0   | Catastrophic Fault Protection fault flag for internal connection to AmP fault manager.                                                                                         |

| VINFB     |              |                    | I.  | Internal - Input voltage measurement for ViUVLO protection                                                                                                                     |

| TSENSE    | PSTSNS       | TMON               | I   | Temperature monitor input from DrMOS Power Stage to C860 controller                                                                                                            |

| PSFLT     | PSFLTB       | FAULT#             | I.  | Open drain fault input pin from DrMOS Power Stage to C860 controller.                                                                                                          |

| ISENSE    | PSISNS       | IMON               | I   | Current monitor input from DrMOS Power Stage to C860 controller.                                                                                                               |

| IREF      | IREFC        | REFIN              | I   | Reference voltage connected to DrMOS power stage REFIN signal and to C860 controller. Recommend using AmP auxiliary 1.2V LDO to drive the signal.                              |

| DCM       | DCMC         | LGCTRL             | 0   | DrMOS power stage lower gate control signal output from DrMOS controller. Used for Discontinuous current mode operation for light load efficiency when available on the DrMOS. |

| EN        |              |                    | I   | Enable DrMOS controller                                                                                                                                                        |

| PWM       | PWMC         | PWM                | 0   | DrMOS power stage gate driver control signal output from DrMOS controller                                                                                                      |

| VFB       | Vfb          |                    | I   | VOUT feedback for DrMOS controller                                                                                                                                             |

Table 2. DrMOS pin interface with AnD7122

# **Electrical Characteristics DrMOS Controller**

$PV_{IN}=V_{IN}=12V$ ,  $T_A=25^{\circ}C$ ,  $Cvdd=10\mu F$ ,  $Cvcc=1\mu F$ , unless otherwise specified

| Parameters                                                                           | Test Condition                                                                                                          | s                      | Min  | Тур  | Max  | Units |

|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------|------|------|------|-------|

| Output Voltage (Vour)                                                                |                                                                                                                         |                        | 0.7  |      | 5.0  | V     |

| Output Voltage Accuracy                                                              | V <sub>IN</sub> range (Including                                                                                        | 6V to 14V              | -2   |      | +1   | %     |

|                                                                                      | load line and temperature variation)                                                                                    | 4.5V to 6V             | -1   |      | +1   | %     |

| Switching frequency (Fsw)                                                            |                                                                                                                         |                        |      | 533  |      | kHz   |

| Switching frequency accuracy                                                         |                                                                                                                         |                        | -5   |      | +5   | %     |

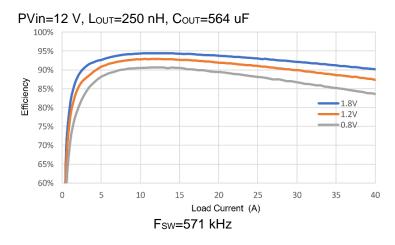

| Efficiency                                                                           | $V_{IN}$ =12V, $V_{OUT}$ =1.8V, $I_{OUT}$ =                                                                             | =10A                   |      | 94   |      | %     |

|                                                                                      |                                                                                                                         |                        |      |      |      |       |

| PROTECTION                                                                           |                                                                                                                         |                        |      |      |      |       |

| ViUVLO, input Undervoltage<br>Lockout range                                          |                                                                                                                         | 4                      |      | 10   | V    |       |

| OCP, Over Current Protection<br>(% Іоит)                                             |                                                                                                                         |                        | 150  |      |      | %     |

| OTP, Over Temperature<br>Protection for AmP device                                   | Shutdown (Power Good g<br>Hysteresis                                                                                    | goes low)              | 125  | 150  | 175  | °C    |

| OVP, Overvoltage Protection<br>trip point range<br>(relative to Vout Setting)        | No resister divider on volt<br>feedback. If a resistor div<br>used, these values will in<br>factor equal to the divider | ider is<br>crease by a | +100 |      | +432 | mV    |

| VoUVLO, output Undervoltage<br>Lockout threshold range<br>(relative to Vout Setting) | No resister divider on volt<br>feedback. If a resistor div<br>used, these values will in<br>factor equal to the divider | -100                   |      | -432 | mV   |       |

| Power Good threshold<br>(relative to Vout Setting)                                   | No resister divider on volt<br>feedback. If a resistor div<br>used, these values will in<br>factor equal to the divider | ider is<br>crease by a | -100 |      | -432 | mV    |

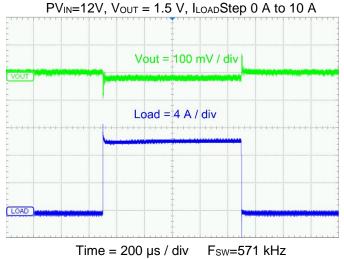

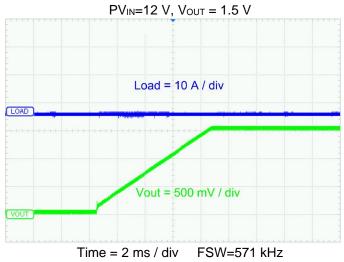

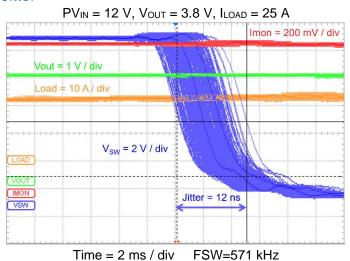

# Typical Characteristics DrMOS Controller

Unless otherwise specified:  $TA = 25^{\circ}C$

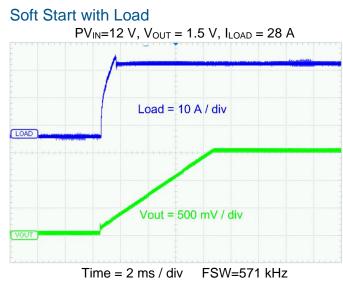

## Transient Response

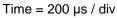

Soft Start No Load

#### Efficiency

Ripple

#### $PV_{\text{IN}} = 12 \text{ V}, \text{ V}_{\text{OUT}} = 0.8 \text{ V}, \text{ I}_{\text{LOAD}} = 30 \text{ A}$

|                                                                                                                 | Vout = 20 mV / div                                                                                              |                                     |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------|

| Inductor = 10 A / div                                                                                           | Ripple = 15 mV                                                                                                  |                                     |

| die eine biefen has so in tille is der bei die an auf ste deret kenslig is                                      | un and a li flenklistnisteli munda se višati un tada a fieta                                                    | dolmai et indica în constitui de de |

|                                                                                                                 | e no esta contrata de la constructiva de la constructiva de la constructiva de la constructiva de la constructi | A DATA DATA A MARKATANA             |

| And the state of the | a di manana di sana di  | -Mart Marth David                   |

| un ette Jasebertund und Alaber<br>out (AC Coupled )                                                             | 1                                                                                                               |                                     |

| out (AC Coupled                                                                                                 |                                                                                                                 |                                     |

| And the state of the | 1                                                                                                               |                                     |

Time = 200  $\mu$ s / div FSW=571 kHz

#### Synchronous Buck Features

- PWM, voltage mode, point-of-load (POL) regulator

- Maximum output current: 10A

- PV<sub>IN</sub>: 4.75V to 14V, V<sub>OUT</sub>: 0.7V to 5.0V

- Switching Frequency: 533kHz

- Adjustable output voltage with 2.4 mV resolution

- Integrated MOSFETs,  $R_{DS(on)}$ : 15m $\Omega$  (10A)

- 1% load regulation

- Efficiency up to 95%

- Internal single pole compensator minimizes external part count

- Protection: Input Undervoltage Lockout, (ViUVLO), Output Undervoltage Lockout, (VoUVLO), Overcurrent (OCP), Overvoltage (OVP)

- Over Temperature Protection (OTP) (part of platform)

- Short-circuit protection (SCP)

- Power-good flag output and Enable input

- Soft start/stop, sequencing, pre-bias startup

- –40°C to +125°C operating junction temperature

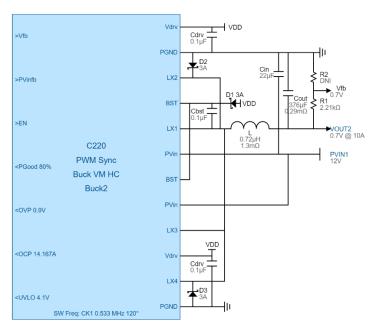

Figure 6. Buck, 10A Typical WebAmP Schematic

# Synchronous Buck Detail

The AnD7122 Synchronous Buck Regulator includes integrated MOSFETs, customizable PWM controller and various protection circuits.

The integrated, low-resistance switching Scalable Integrated MOSFETs (SIM) provide up to 10A output current.

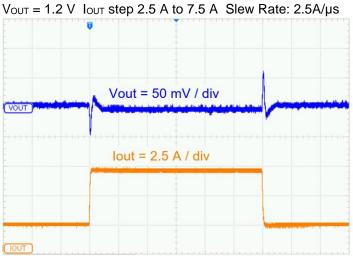

Output voltage feedback is compared against an internal reference using a high-performance, voltage-error digitizer that provides tight voltage regulation accuracy under transient conditions. Pulse-width modulated (PWM), voltage-mode regulation is implemented with PID compensation. The switching frequency is generated internally via an oscillator and is fixed at 533kHz.

The customizable output voltage is specified by the WebAdapter tool or an external resistor divider. The regulator has customizable control and status pins including enable input, power-good output, and output flags to signal when the system triggers an overvoltage (OVP), overcurrent (OCP), or undervoltage lockout (UVLO) condition.

The soft-start and soft-stop slew rates are also specified at 4 ms. Additional sequencing options are available by using the WebAdapter tools or jumpers.

The AnD7122 uses predefined power components from the AmP power library. This allows an easy migration to On-Demand PMIC. The buck converters are based on the C220 power component.

## Recommended Operating Conditions Synchronous Buck

Over operating free-air temperature range

| Symbol            | Parameter            | Min  | Тур | Max | Unit |

|-------------------|----------------------|------|-----|-----|------|

| PVIN              | Power Input Voltage  | 4.75 |     | 14  | V    |

| I <sub>Lmax</sub> | Load Current Maximum |      |     | 10  | A    |

| V <sub>IN</sub>   | Bias Supply          | 4.75 |     | 14  | V    |

## Electrical Characteristics Synchronous Buck

$PV_{IN} = V_{IN}=12V$ , T<sub>A</sub>=25°C, Cvdd=10µF, Cvcc=1µF, unless otherwise specified

| Parameters                                                                                | Test Cond                                                  | itions                   | Min  | Тур | Max  | Units |

|-------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------|------|-----|------|-------|

| Output Voltage (Vout) Range                                                               |                                                            |                          | 0.7  |     | 5    | V     |

| Output Voltage Regulation                                                                 | V <sub>IN</sub> range                                      | 6V to 14V                | -2   |     | +1   | %     |

|                                                                                           | (Including load line and temp. variation)                  | 4.5V to 6V               | -1   |     | +1   | %     |

| Switching frequency (Fsw)                                                                 |                                                            |                          |      | 533 |      | kHz   |

| Switching frequency accuracy                                                              |                                                            |                          | -5   |     | +5   | %     |

| MOSFET switch on-resistance (R <sub>DS(on)</sub> )                                        |                                                            |                          |      | 15  |      | mΩ    |

| Efficiency                                                                                | V <sub>IN</sub> =12V, V <sub>OUT</sub> =1.2V, I<br>Iout=3A | F <sub>sw</sub> =533kHz, |      | 83  |      | %     |

| Input Shutdown current (V <sub>IN</sub> )                                                 | EN = 0V                                                    |                          |      | 13  |      | mA    |

| Input quiescent current (PV <sub>IN</sub> )                                               |                                                            |                          |      | 7   |      | mA    |

| PROTECTION                                                                                |                                                            |                          |      |     |      |       |

| ViUVLO, input Undervoltage<br>Lockout                                                     |                                                            |                          | 4    |     | 10   | V     |

| OCP, Over Current Protection<br>(% Ιουτ)                                                  |                                                            |                          |      | 142 |      | %     |

| OTP, Over Temperature<br>Protection                                                       | Shutdown (Power Go<br>Hysteresis                           | od goes low)             | 125  |     |      | °C    |

| OVP, Overvoltage Protection<br>trip point range<br>(relative to Parameter Setting)        |                                                            |                          | +100 |     | +432 | mV    |

| VoUVLO, output Undervoltage<br>Lockout threshold range<br>(relative to Parameter Setting) |                                                            |                          | -100 |     | -432 | mV    |

| Power Good threshold<br>(relative to Parameter Setting)                                   |                                                            |                          | -100 |     | -432 | mV    |

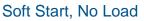

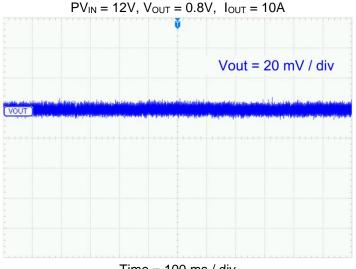

### Typical Characteristics Synchronous Buck

Unless otherwise specified: T\_A = 25°C, F\_{SW} = 533 kHz, L\_{OUT} = 1.2 \mu H, C\_{OUT} = 376 \mu F

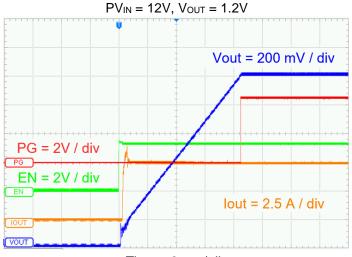

#### **Transient Response**

## Load Regulation Percentage Error

#### Soft Start, Load = 5A

Time = 2 ms / div

Vout Ripple

Time = 100 ms / div

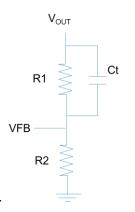

#### Inductor Selection

Based on output voltage target, the Table 3 shows recommended inductor and compensation capacitor value providing optimal performance.

Ct capacitance is required for higher output voltage range, in parallel with R1 resistor, to improve stability of the compensation without changing the PID coefficients.

As an example, for an output voltage ranging between 1.2 V to 2.5 V, use a 1.5uH inductor and capacitance Ct of 2.2nF.

Figure 7. VOUT feedback network

| VIN = 12V |                    | <u>fsw</u> = 530k                                            | Hz-571kHz           |                     |  |

|-----------|--------------------|--------------------------------------------------------------|---------------------|---------------------|--|

| VOUT      | L=0.68uH<br>Ct=N/A | L=1uH<br>Ct=N/A                                              | L=1.5uH<br>Ct=2.2nF | L=2.2uH<br>Ct=4.7nF |  |

| 0.7V      |                    |                                                              |                     |                     |  |

| 1.0V      |                    |                                                              |                     |                     |  |

| 1.2V      |                    |                                                              |                     |                     |  |

| 1.5V      |                    |                                                              |                     |                     |  |

| 1.8V      |                    |                                                              |                     |                     |  |

| 2.5V      |                    |                                                              |                     |                     |  |

| 3.3V      |                    |                                                              |                     |                     |  |

| 5V        |                    |                                                              |                     |                     |  |

|           | L                  | value is in the                                              | e ideal range       |                     |  |

|           | L valı             | L value just outside the ideal range, system works correctly |                     |                     |  |

Table 3. Inductor selection

## V<sub>OUT</sub> Resistor Settings

$V_{\text{OUT}}$  voltages for Buck1 and Buck2 POLs are set by the resistors R1 and R2. The AnD7122 internal feedback reference, VFB, is 0.7 V for Buck1 and Buck2 with feedback resistor recommended values of

$$R1 = 2.21 \text{ k}\Omega$$

$$R2 = \text{DNI (Do Not Install).}$$

For  $V_{\text{OUT}}$  values greater the 0.7 V, use the following resistor divider equations:

$$\label{eq:R1} \begin{split} &\mathsf{R1} = 2.21 \; \mathsf{k}\Omega \\ &\mathsf{R2} = \mathsf{VFB} \; \mathrm{x} \frac{\mathsf{R1}}{(\mathsf{Vout} - \mathsf{VFB})} \; \mathsf{k}\Omega \end{split}$$

1% resistors are recommended for best accuracy. A resistor calculator for closest E96 1% value is provided by the WebAdapter Software Tool.

These resistor values determine the actual  $V_{OUT}$  voltage calculated as shown above. A DNI value indicates "Do Not Install". R1 and R2 values may now be applied to the Reference Designators for the user's board design.

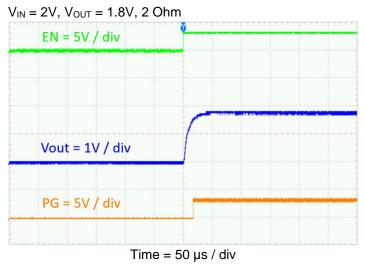

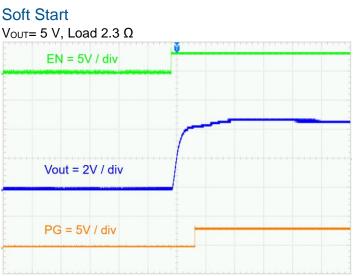

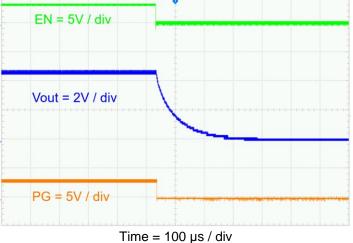

#### Start-up and Shutdown

Start-up and shutdown are controlled by the EN digital port. When EN goes high the output voltage,  $V_{OUT}$ , will ramp up according to the Soft Start ramp time. When EN goes low, the output voltage,  $V_{OUT}$ , will ramp down according to the Soft Start preset ramp time.

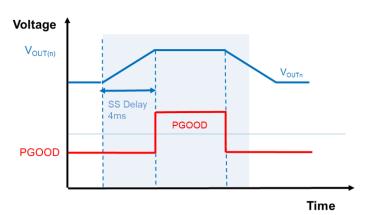

#### PGOOD

The power-good, PGOOD, of all Synchronous Buck Converters are combined to generate the global Power Good signal, indicating the output voltage regulation status. PGOOD goes high on power-up after completion of all the Soft Start time (Figure 8) and when all Faults are cleared . PGOOD will pull low either when  $V_{OUT}$  falls below the preset condition (80% of the  $V_{OUT}$ ) or when faults occur. These faults include OCP fault , OVP fault , UVLO (both input and output) faults and OTP thermal shutdown fault. PGOOD will also go low if EN goes low.

Figure 8 Soft-start and shutdown

### Sequencer

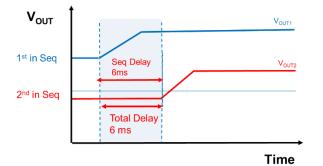

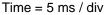

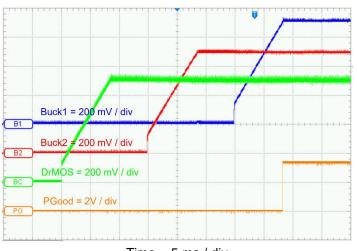

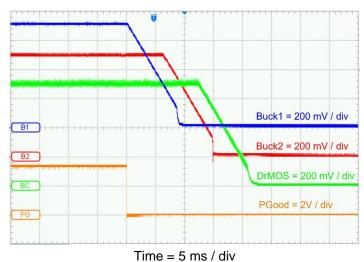

The AnD7122 contains a sequencer that can operate either based on time delay or based on power good signal. The selection of power good or time delay is based on the setting of the TIME control pin 28. When the TIME control pin is high, the sequencer is based on time delay. When the TIME control pin is low, the sequencer is based on the PGood signal.

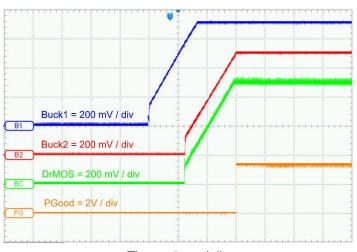

The sequencing delay is programmable from 3 ms to 16 ms using WebAdapter advanced mode. By default, it is set to 6 ms. The soft start is set to 2/3 of the programmed sequencing delay value allowing enough time for the previous sequencer to be fully ON before the next sequence starts.

The sequencer is activated by setting the SEQ\_EN to high. TIME, CTL and OUT pins have an internal pull-up resistor, so they can be left floating (or not connected) to be in high state. Low signal can be set with a connection to ground (GND).

#### TIME Mode

TIME Mode is specified when the TIME pin is in a high state as defaulted in the AnD7122 . In this mode, each Buck[n] regulator tuns ON with a Soft Start when Enable[n], goes high. On completion of Soft Start period, Sequencer Delay remains before Enable[n+1] goes high, beginning the sequence for Buck[n+1]. In the example below, the sequencing delay is set to 6 ms .

Figure 9. Soft-start TIME mode

#### Sequencer Pin Connections

POL power-on and power-off sequences for Buck1 and Buck2 are set by the sequence Pin Connections specified in the wire connection in Table 4. Apply these connections to the AnD7122 board design.

In time mode, the outputs (OUT1, OUT2) of the sequencer need to be connected to the appropriate Enable pins for each Buck.

| Sequen  | Sequence Output |               | able Input |  |

|---------|-----------------|---------------|------------|--|

| Signal  | AnD7122         | Signal AnD712 |            |  |

| Name    | Pin Number      | Name          | Pin Number |  |

| OUT1    | 60              | EN1 57        |            |  |

| T 1 1 0 |                 | 0             | · TIM 15 1 |  |

Table 4. Sequencer pin connections in TIME mode

## **TIME/CTL Pin Connections**

The control pins CTL0 must be held high as indicated in the wire connection Table 5.

Apply these conditions to the AnD7122 board design.

| Co     | ntrols | Signal |                    |

|--------|--------|--------|--------------------|

| Signal | Pin    | Level  | Function           |

| Name   | Number |        |                    |

| TIME   | 28     | High   | TIME Mode          |

| CTL0   | 56     | High   | Sequence<br>Select |

Table 5. TIME and CTL pin behaviour in TIME mode

#### PGOOD Mode

The user has also the option to set the sequencing using Power good signal.

PGOOD Mode is selected when the TIME pin is in a low state as indicated by the "GND" Signal Level specified in the wire connection table below. Control pin CTL0 specifies the selected sequence.

| Co     | ntrols | Signal |            |

|--------|--------|--------|------------|

| Signal | Pin    | Level  | Function   |

| Name   | Number |        |            |

| TIME   | 28     | Low    | PGOOD Mode |

| CTL0   | 56     | High   | Sequence   |

|        |        |        | Select     |

Table 6. TIME/CTL pin connections

In this mode, each Buck[n] regulator begins a 4 ms Soft Start when Enable[n], goes high. On completion of Soft Start, PGOOD[n] goes high and starts the programmed Sequencer Delay followed by Enable[n+1] going high, beginning the sequence for Buck[n+1]. If the user sets the sequencer delay to 6ms, The total cycle delay is 4ms + 6ms = 10ms per Buck as shown in the timing diagram below.

Figure 10. PGOOD mode

# PGOOD and Sequencer Pin Connections

The Control pin, CTL0, specifies the selected sequence.

| CTL0 | Seq1   | Seq2   |

|------|--------|--------|

| High | Buck 1 | Buck 2 |

| Low  | Buck2  | Buck 1 |

Table 7. PGOOD sequence

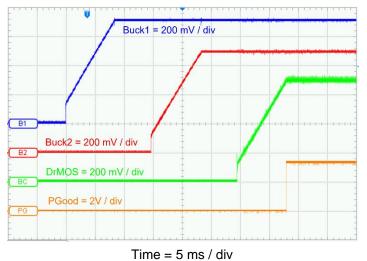

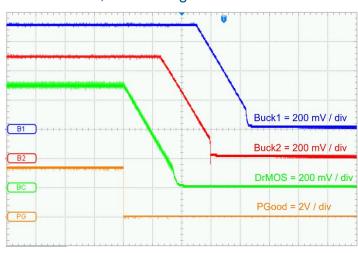

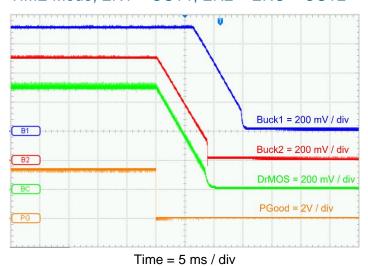

# Sequencer Example Waveforms

#### PGOOD Mode, CTL0 = high

## PGood Mode, CTL0 = low

Time = 5 ms / div

#### TIME Mode, EN1 = OUT1, EN2 = ENC = OUT2

Time = 5 ms / div

#### PGood Mode, CTL0 = low

# TIME Mode, EN1 = OUT1, EN2 = ENC = OUT2

PGood Mode, CTL0 = high

## High current LDO Features

- Linear, constant voltage, low-dropout regulator

- Adjustable V<sub>OUT</sub> from 0.6 V to 3.3 V

- Maximum output current: 1 A

- 1% typical line and load regulation

- Very low dropout :100 mV dropout

- Short-circuit protection (SCP)

- Protection: Overcurrent (OCP), and Over Temperature (OTP)

- Power-good and OCP flag outputs and Enable input

- Soft start/stop

- -40°C to +125°C operating junction temperature

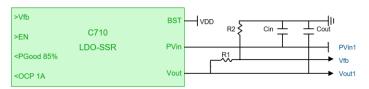

Figure 11: LDO Typical WebAmP Schematic

## Product Detail – High current LDO

The AnD7122 has 2 high current LDOs which are parts of the AmP platform power components (C71x: C710 or C715)

The LDO is a 1 A general purpose low-dropout (LDO) regulator. The integrated current sense provides overcurrent protection (OCP) and short circuit protection.

The customizable output voltage is specified by the power engineer during customization using AnDAPT's cloudbased WebAdapter development software or using resistor divider as described in VOUT Resistor Settings.

The LDO also incorporates a soft start feature to protect against inrush current. Sequencing options are available by interconnecting signals EN to provide dependencies and delays between each sequence step. See C71X datasheets for more LDO details.

# System Characteristics

Table 8 lists the system characteristics for the High current LDOs Power Component when implemented in an AnDAPT AmP device.

| Parameters                                | Min          | Тур | Max | Units |

|-------------------------------------------|--------------|-----|-----|-------|

| Input Drain Voltage (PV <sub>IN</sub> ) * | Vout+<br>Vdo |     | 17  | V     |

| Output Voltage (V <sub>OUT</sub> )        | 0.6          |     | 3.3 | V     |

| Output Current (IOUT)                     |              |     | 1   | Α     |

| Dropout Voltage (VLDO)                    |              |     |     |       |

| @ Vout =1.8V                              |              |     |     |       |

| I <sub>DS</sub> =0.1A                     |              | 20  |     | mV    |

| I <sub>DS</sub> =1A                       |              | 100 |     | mV    |

| Dropout Voltage (VLDO)                    |              |     |     |       |

| @ Vout =3.3V                              |              |     |     |       |

| I <sub>DS</sub> =0.1A                     |              | 20  |     | mV    |

| I <sub>DS</sub> =1A                       |              | 200 |     | mV    |

| Voltage regulation                        |              | 0.5 |     | %     |

| Current Limit – OCP                       | 1            |     |     | А     |

| Cout                                      | 69           |     |     | μF    |

\*Note: The maximum power dissipation for the LDO,  $(V_{\text{IN}}\text{-}V_{\text{OUT}})^*I_{\text{OUT}},$  is limited to 1.5W

Table 8 LDO System Characteristics

## VOUT Resistor Settings

$V_{\text{OUT}}$  voltages for LDO1 and LDO2 are set by the resistors R1 and R2. The AnD7122 internal feedback reference, VFB, is 0.7 V for LDO1 and LDO2 with feedback resistor recommended values of

$$R1 = 2.21 \text{ k}\Omega$$

$R2 = DNI (Do Not Install)$

For  $V_{\text{OUT}}$  values greater the 0.6 V, use the following resistor divider equations:

$$R1 = 2.21 \text{ k}\Omega$$

$$R2 = VFB \text{ x} \frac{R1}{(Vout - VFB)} \text{ k}\Omega$$

1% resistors are recommended for best accuracy. A resistor calculator for closest E96 1% value is provided by the WebAdapter Software Tool.

These resistor values determine the actual  $V_{OUT}$  voltage calculated as shown above. A DNI value indicates "Do Not Install". R1 and R2 values may now be applied to the Reference Designators for the user's board design.

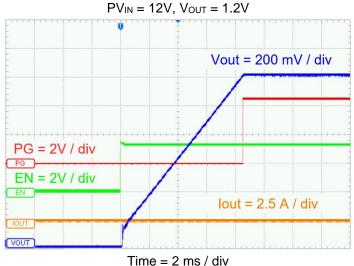

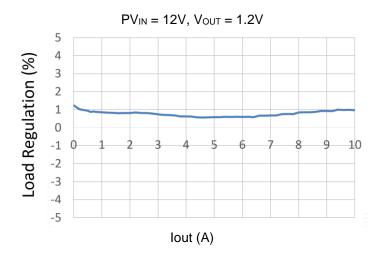

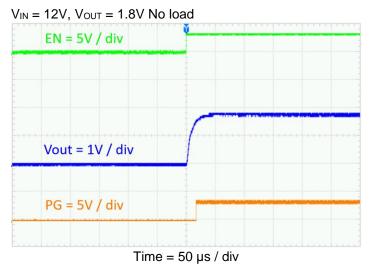

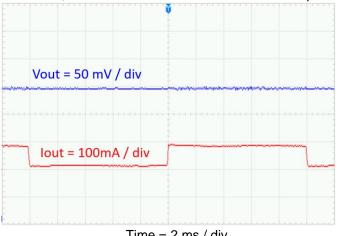

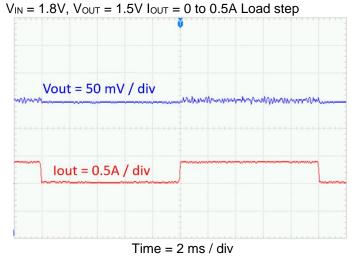

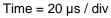

## Typical Characteristics High Current LDO

Unless otherwise specified: TA =  $25^{\circ}$ C, C<sub>OUT</sub> =  $69 \mu$ F

## Soft Start

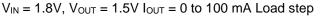

## **Transient Response**

Time = 2 ms / div

# Soft Start

**Transient Response**

# **Transient Response C715**

$V_{IN} = 12V$ ,  $V_{OUT} = 3.3V$   $I_{OUT} = 0$  to 1A Load step

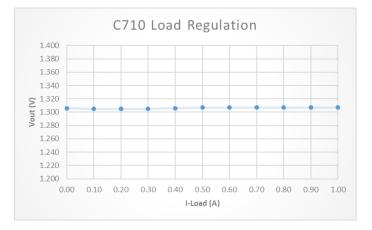

# Load Regulation

$PV_{IN} = 1.5V, V_{OUT} = 1.3V$

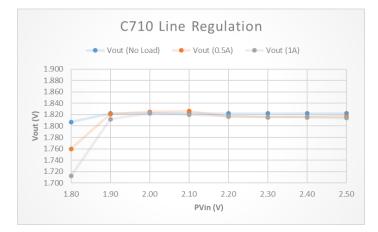

# Line Regulation

$V_{OUT} = 1.8V$

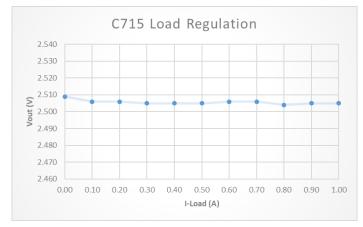

## Load Regulation

$PV_{IN} = 2.8V, V_{OUT} = 2.5V$

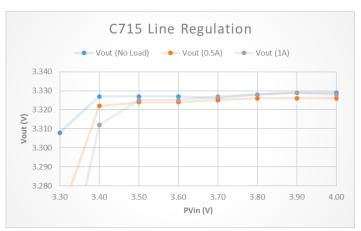

# Line Regulation

Vout = 3.3V

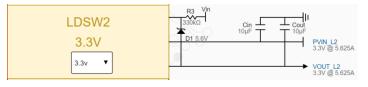

#### High Current Load Switches

The AnD7122 has 2 high current load switches which are parts of the AmP platform power components: (C750 or C755)

The load switches provide power domain isolation. It contains a low on-resistance N-channel MOSFET that supports up to 6A of continuous current and minimizes power loss. In addition, the device features over current (OCP) and over voltage protection (OVP) to protect the device against fault conditions.

The Load Switch is controlled by an on and off input, which is capable of interfacing directly with low-voltage control signals.

The load switch has control and status pins including an enable input, a power-good output. The Load Switch parameters are specified by the power engineer using AnDAPT's cloud-based WebAdapter<sup>™</sup> development software.

#### Features

- Output voltage from 0.5 V to 5 V

- Low RDSon MOSFET: 30 m  $\!\Omega$

- Maximum output current: 6 A

- · Soft-start slew rate to control inrush current

- Protections: OCP, OVP, reverse-current

In AnD7122, the load switch output voltages can be adjusted using WebAdapter in advanced mode.

The default value is 0.6 V for  $V_{\text{OUT}}$  and 6 A for the output current.

#### **Output Capacitance**

The  $C_{OUT}$  determines the slew rate of the output voltage during soft start. The default value is 10  $\mu$ F. Slew rate (SR) is a function of the capacitance and the current :

SR = IOUT/COUT

For 6 A, 10 uF, the slew rate will be 0.6 V/us

The Soft-start feature is always enabled and allows a controlled ramp of the output based on the value set by  $C_{\text{OUT}}.$

#### Input Capacitance

The input capacitance  $C_{IN}$  is used to reduce the sensitivity of the circuit to the PCB layout, especially when high source impedance or long input traces are encountered.

A 10uF minimum capacitance is recommended.

#### **Fault Protection**

The load switches are protected against damage due to excessive power dissipation by current limit (OCP) and output voltage protection (OVP).

When the output load exceeds the over current limit, the device turns off.

For OCP, the load switches current limits are set to a minimum of 5.5 A.

#### Vout Setting

By default, the  $V_{\mbox{\scriptsize OUT}}$  Sense is internal for the load switches.

For  $V_{OUT}$  voltage greater than 2.5 V, a resistor and a Zener diode are recommended additions as shown in Figure 12.

Figure 12. Typical load switch WebAdapter interface

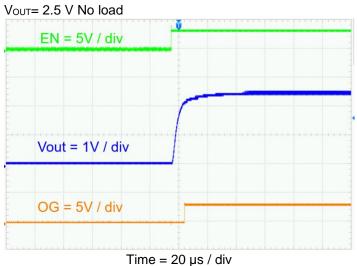

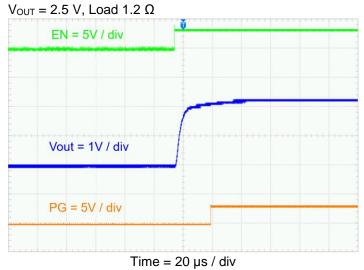

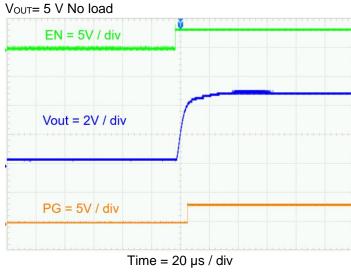

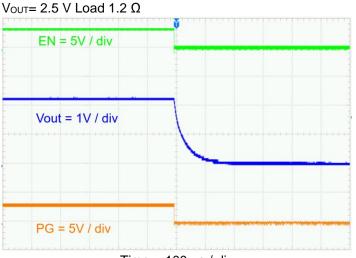

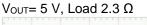

# Typical Characteristics High Current Load Switch

Unless otherwise specified:  $T_{\text{A}}$  = 25°C,  $C_{\text{OUT}}$  = 10  $\mu F$

## Soft Start

Soft Stop

Time = 100  $\mu$ s / div

## Soft Stop

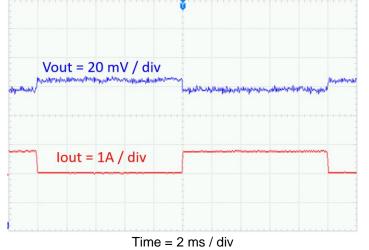

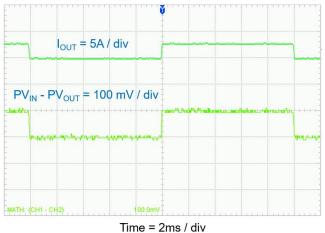

## **Transient Response C750**

$\mathsf{PV}_{\mathsf{IN}}$  = 5V, ( $\mathsf{PV}_{\mathsf{IN}}$  -  $\mathsf{PV}_{\mathsf{OUT}}$ ) = 100 mV,  $\ \mathsf{I}_{\mathsf{OUT}}$  = 0 to 3A Load step

# **Transient Response C750**

Time = 2ms / div

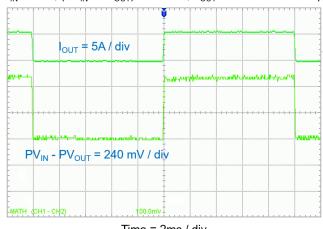

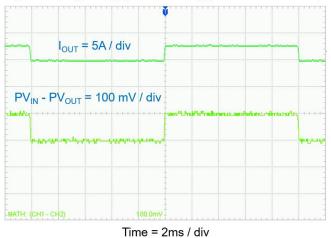

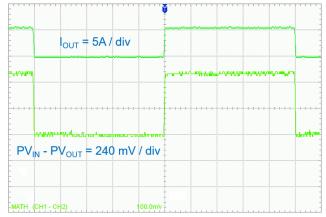

## **Transient Response C755**

$PV_{IN} = 5V$ , ( $PV_{IN} - PV_{OUT}$ ) = 100 mV,  $I_{OUT} = 0$  to 3A Load step

## **Transient Response C755**

$\mathsf{PV}_\mathsf{IN}$  = 1.8V, ( $\mathsf{PV}_\mathsf{IN}$  -  $\mathsf{PV}_\mathsf{OUT}$ ) = 240 mV,  $\ \mathsf{I}_\mathsf{OUT}$  = 0 to 6A Load step

Time = 2ms / div

$PV_{IN}$  = 2.5V, ( $PV_{IN}$  -  $PV_{OUT}$ ) = 240 mV,  $I_{OUT}$  = 0 to 6A Load step

#### Integrated Auxiliary LDOs

The AnD7122 has 4 integrated auxiliary LDOs which have default output voltages of 3.3 V, 2.5 V, 1.8 V, and 1.2 V. The input voltage of the four LDOs is from the internal 4.5 V bias voltage or externally supplied 5 V on the VDD pin. A decoupling capacitance of 10  $\mu$ F minimum must be connected to the output of the LDO. The pin locations of these integrated LDOs, are fixed and cannot be modified by WebAmP Tools.

Electrical characteristics for Integrated Auxiliary LDOs are shown below in Table 9.

Two of these LDOs (LDOa and LDOb) output voltages are programmable by using the WebAdapter tool.

## **Electrical Characteristics Integrated Auxiliary LDOs**

VIN=12V, TA=25°C, Cvdd = Cvcc = Cldoa = Cldob= C3v3 = 10µF unless otherwise specified

| Symbol            | Parameter                      | Condition                       | Min   | Тур | Max   | Unit |

|-------------------|--------------------------------|---------------------------------|-------|-----|-------|------|

| LDO1V2            | LDO 1.2V output voltage        | Icc=0mA, V <sub>IN</sub> =4.5V  | 1.164 | 1.2 | 1.236 | V    |

| Rocc              | LDO 1.2V equivalent resistance |                                 |       | 350 |       | mΩ   |

| Icc               | LDO 1.2V output current        |                                 |       |     | 200   | mA   |

| LDOa              | LDO 1.8V output voltage        | I1V8=0mA, V <sub>IN</sub> =4.5V | 1.746 | 1.8 | 1.854 | V    |

| R <sub>01V8</sub> | LDO 1.8V equivalent resistance |                                 |       | 350 |       | mΩ   |

| I1V8              | LDO 1.8V output current        |                                 |       |     | 200   | mA   |

| LDOb              | LDO 2.5V output voltage        | I2V5=0mA, V <sub>IN</sub> =4.5V | 2.425 | 2.5 | 2.575 | V    |

| R <sub>02V5</sub> | LDO 2.5V equivalent resistance |                                 |       | 350 |       | mΩ   |

| lcc               | LDO 2.5V output current        |                                 |       |     | 200   | mA   |

| LDO3V3            | LDO 3.3V output voltage        | I3V3=0mA, V <sub>IN</sub> =4.5V | 3.201 | 3.3 | 3.399 | V    |

| R <sub>O3V3</sub> | LDO 3.3V equivalent resistance |                                 |       | 350 |       | mΩ   |

| I3V3              | LDO 3.3V output current        |                                 |       |     | 200   | mA   |

Table 9. Integrated auxiliary LDO characteristics

## **Additional Resources**

- AnDAPT AmP Platform datasheet

- Power Component datasheets

## ESD CONSIDERATIONS

Establish and use (Electrostatic Damage) ESD-safe handling precautions when unpacking and handling ESD-sensitive devices. Store ESD sensitive devices in ESD safe containers until ready for use. The Tape-and-Reel moisture-sealed bag is an ESD approved barrier. The best practice is to keep the units in the original moisture sealed bags until ready for assembly. AnDAPT products are qualified to meet at least 500 V ESD-MM (Machine Model) 2000 V ESD-HM (Human Body Model). Restrict all device handling to ESD protected work areas that measure less than 400 V static charge. Ensure that all workstations and personnel are properly grounded to prevent ESD.

#### Assembly Recommendation

For part placement, please use standard pick and place machine with  $\pm$  0.05 mm accuracy. Mount the device with slower speed and higher force. Place the package 1 ~ 2 mils into the paste. The device package has excellent self-alignment during solder reflow if a minimum of 75% of the lead diameter intersect with the pad.

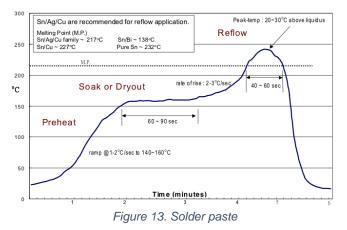

#### Solder Paste

The screen-printing quantity of solder paste is a key factor in producing high yield assemblies. Recommended solder paste alloy is Sn/Ag/Cu family for lead-free application. Low residue and no clean flux are recommended. Particle size type IV (25 ~ 38  $\mu$ m) is preferred to improve printing performance. Particle size type III (25 ~ 45  $\mu$ m) also is acceptable.

#### **Solder Stencils**

The contrast between large thermal pads and small terminal pads of the QFN package can present a challenge in production and even solder line thickness. The precise volume of solder paste deposited onto the device land pattern is controlled by the stencil thickness and the opening geometry. Stencil alignment accuracy and consistent solder volume transfer is critical for uniform reflow- solder processing. The solder joint thickness for QFN package terminal pads should be 50 - 75 µm. Stencil recommended type is laser cutting stainless steel with thickness of 100 ~ 150  $\mu$ m (125  $\mu$ m as a guide). The actual thickness of a stencil is depending on other SMD components on the PCB. Metal blade or polymer with 90-degree hardness squeegee is recommended. Aperture size for terminal pad should have aspect ratio (width / thickness) of greater than 1.5 and area ratio (Area of aperture opening / aperture wall area) of greater than 0.66. The stencil aperture is typically designed to match the pad size on the PCB 1 to 1. For fine pitch components of 0.5mm and below it may be necessary to reduce the stencil aperture length by 20%. An oval-shaped opening should be used to get the optimum paste release and rounded corners to minimize clogging. Positive taper walls (5-degree tapering) with bottom opening larger than the top is recommended. Small multiple openings should be used instead of one big opening. 60% ~ 85% solder paste

coverage is recommended to reduce the chance of having short connection.

#### **Reflow Specification**

AnDAPT products are qualified in accordance with IPC/JEDEC J-STD-020D.1. This standard classifies proper packaging, storage and handling to avoid subsequent thermal and mechanical damage during the solder-reflow attachment phase of PCB assembly. Check solder paste data sheet for any additional or difference instruction. Using a forced convection reflow oven with nitrogen is recommended. Also, the reflow oven should have equal or less than  $\pm$  5°C temperature uniformity. The recommended reflow profile for lead-free solder paste shown in Figure 13.

#### Compliance

#### **Environmental Compliance**

AnDAPT products are RoHS and Green compliant. AnDAPT products are in full environmental compliance as evidenced by our Materials Declaration Data Sheets (MDS). The MDS report, along with support documentation consisting of Material Safety Data Sheets (MSDS) and analytical reports for each homogeneous element of the product are available upon request.

#### **DRC** Compliance

AnDAPT products use materials that comply with DRC (Democratic Republic of the Congo) Conflict-Free Smelter and Mines requirements to meet the SEC implementation of Dodd–Frank Section 1502.

#### **Compliance Declaration Disclaimer**

AnDAPT believes this compliance information to be correct but cannot guarantee accuracy or completeness. Conformity documents for the above component constitutes are on file. AnDAPT subcontracts manufacturing and the information contained herein is based on data received from vendors and suppliers, which has not been validated by AnDAPT.

# Internal AnD7122 PMIC Blocks and Resources

Each Power Component uses several blocks and resources that are available as part of the AND7122 PMIC. Listed below is a description of blocks and resources that are used to create Buck regulators.

#### Noise-immune references - Nrefs

- 10-bit, 0.1% resolution for <0.5% regulation

- Curvature compensated band-gap trim

- Precision across process, temperature

Nrefs provide reference voltages to analog GPIOs, Adaptive Digitizers, Threshold Comparators, In Amp, SIM linear LDO and SIM protect. On power-up, Nrefs are configured to voltages specified by the user.

#### Compensator Memory - CRAM

- Flexible, high bandwidth PID

- Adjust gain/phase margin, bandwidth

- Symmetric, binary scaling cuts memory by four

- Adaptive, dual regulation, 1 or 2 poles

The CRAM provides digital compensation to integrated MOSFETs implementing switching regulator functions including buck, boost and multi-phase regulators. The CRAM implements the Proportional Integral Derivative algorithm, PID, as in the following equation:

# $$\begin{split} \mathsf{P}[\mathsf{n}] &= \mathsf{P}[\mathsf{n}\text{-}1]^*\mathsf{a}1 + \mathsf{P}[\mathsf{n}\text{-}2]^*\mathsf{a}2 + \mathsf{E}[\mathsf{n}]^*\mathsf{a} + \mathsf{E}[\mathsf{n}\text{-}1]^*\mathsf{b} + \mathsf{E}[\mathsf{n}\text{-}2]^*\mathsf{c} \\ 1 \text{ pole: } \mathsf{a}1 &= \mathsf{1}, \quad \mathsf{a}2 &= \mathsf{0} \quad 2 \text{ poles: } \mathsf{a}1 &= \mathsf{0.5}, \, \mathsf{a}2 &= \mathsf{0.5} \\ & \mathsf{E}[\mathsf{n}] &= \mathsf{V}\mathsf{ref}\text{-}\mathsf{V}_\mathsf{OUT}[\mathsf{n}] \end{split}$$

#### Precision Modulation Timers - PMTs

- 11-bit, 1.25 ns resolution

- Static, dynamic or stopwatch

Lowers bias current, system freq.

The PMT provides precision delays for Pulse Width Modulation (PWM), MOSFET turn-on, turn-off timing and sensor sample timing. Delays may be fixed or dynamic ranging from nanoseconds, milliseconds, microseconds to seconds with resolution less than one nanosecond.

#### Adaptive Digitizer – ADi

- Digitize feedback Error

- Highest precision at reference point

- Low cost & fast sampling

The ADi converts differential analog signals from GPIOs or Nrefs and deliver up to 10-bits digital signed magnitude numbers to the digital fabric. Each ADi consists of two digitizers to provide highest speed and precision.

#### Scalable Integrated MOSFET-SIM

•  $R_{DSON}$  of 30 m $\Omega$

The SIM in switch mode provides integrated MOSFETs to perform switching regulator and gate driver functions. The MOSFET gate may be driven directly from fabric, from the Gate Flip-flop or adjacent SIM Gate Flip-flops. The Gate Flip-flop is set from the fabric, then reset from fabric, current sense peak/valley/limit1/limit2 or zero detect. The MOSFET gate may be segmented in up to 15 individual gates to reduce gate capacitance. The GateOn signal detects the actual on-status of the MOSFET gate for precise timing control of Hi-side and Lo-side topologies.

SIM in linear mode provides integrated MOSFETs to perform LDO and Load Switch functions. The MOSFET gate is driven by a linear Operational Amplifier to implement linear, voltage or current, regulators. Op Amp inputs include Source, drain voltage or current and Analog Fabric including programmable references (Nrefs).

Figure 14: PMIC Blocks and Resources Example - Buck Regulator

#### DrMOS Controller, Buck, LDO & LDSW PMIC

AnD7122

|                              | SYMBOL | COM  | MON DIMENS | SIONS |

|------------------------------|--------|------|------------|-------|

|                              |        | MIN. | NOR.       | MAX.  |

| TOTAL THICKNESS              | Α      |      |            | 0.7   |

| SUBSTRATE THICKNESS          | A1     |      | 0.11       | REF   |

| MOLD THICKNESS               | A2     |      | 0.53       | REF   |

| BODY SIZE                    | D      | 4.9  | 5          | 5.1   |

| BODT SIZE                    | E      | 4.9  | 5          | 5.1   |

| LEAD WDTH                    | W1     | 0.15 | 0.2        | 0.25  |

| LEAD WDTH                    | W2     | 0.2  | 0.25       | 0.3   |

| LEAD LENGTH                  | L1     | 0.15 | 0.2        | 0.25  |

| LEAD LENGTH                  | L2     | 0.2  | 0.25       | 0.3   |

| LEAD LENGTH                  | L3     | 1    | 1.05       | 1.1   |

| LEAD PITCH                   | e      |      | 0.4        | BSC   |

| LEAD COUNT                   | n      |      | 65         |       |

| FREE RALL OFWER TO OFWER     | D1     |      | 4.5        | BSC   |

| EDGE BALL CENTER TO CENTER   | E1     |      | 4.5        | BSC   |

| DODY OFNITED TO CONTLOT DALL | SD     |      | 0.2        | BSC   |

| BODY CENTER TO CONTACT BALL  | SE     |      | 0.2        | BSC   |

| PACKAGE EDGE TOLERANCE       | aaa    |      | 0.1        |       |

| MOLD FLATNESS                | bbb    |      | 0.1        |       |

| COPLANARITY                  | ddd    |      | 0.08       |       |

|                              | eee    |      |            |       |

| BALL OFFSET (PACKAGE)        |        |      |            |       |

# Solder Stencil – QF65 5x5 mm

Download files: <u>AmP8DQF65footprint.zip</u>

#### Errata

| Date       | description                             |  |

|------------|-----------------------------------------|--|

| 12/28/2018 | SIM Pin (MOSFET DRV-Drain) ESD 750V HBM |  |

|            |                                         |  |

**Revision History**

| Date       | Revision        |  |

|------------|-----------------|--|

| 11/04/2019 | Initial release |  |

|            |                 |  |

www.AnDAPT.com

#### Trademarks

© 2019 AnDAPT, Inc., the AnDAPT logo, AmP, WebAmP, AmPLink, AmPScope, WebAdapter and other designated brands included herein are trademarks of AnDAPT in the United States and other countries. All other trademarks are the property of their respective owners.