# PWM Single-Phase DrMOS Controller

# Power Component: C865\_B

# **Product Description**

The C865\_B Power Component is a customizable, single-phase, voltage-mode DrMOS controller designed for point-ofload (POL) applications. Combine the C865\_B with other Power Components to create a custom-defined, AnDAPT AmP on-demand PMIC.

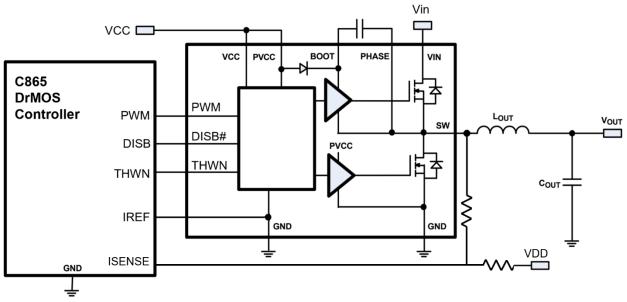

Power components are software components, accessible through WebAmP<sup>™</sup>, allowing users to create their own PMIC. The C865\_B has been developed to interface with industry-standard DrMOS devices using DCR current sense such as the onsemi NCP302035\*/2040\*/2150\*/FDMF5820DC and Alpha & Omega Semiconductor. AOZ5339QI/5636QI/5237QI\* that have similar pinout. The DrMOS is a fully integrated power stage that integrates a high side and low side MOSFET and a high-performance driver with integrated bootstrap FET. Maximum output current will be based on the selected external DrMOS and on the thermal design of the specific application. Development Board, DB3 supports the above DrMOS devices.

# Features

- PWM, voltage mode, DrMOS controller

- Adjustable output voltage with down to 2.5 mV resolution

- 1% voltage accuracy

- Efficiency up to 94%

- Adjustable switching frequency 533 to 1000 kHz

- Adaptable bandwidth & phase margin

- Adjustable protections: Input Undervoltage Lockout (ViUVLO), Output Undervoltage Lockout (VoUVLO), Overcurrent Protection (OCP), Overvoltage Protection (OVP), Over temperature Protection (OTP), Short-circuit Protection (SCP)

- Power-good flag output and Enable input

- Controller junction temperature range -40°C to +125°C

- Component included in the WebAmP<sup>™</sup> development tool

# **Applications**

- On-demand power management, multi-rail power integration

- Powering server, processor, memory, storage, network switcher and router platforms

- FPGA, processor, SSD, subsystem power control & sequencing

### Figure 1. C865\_B Power Component

| >VINFB  |                                 | PWM>   |

|---------|---------------------------------|--------|

| >EN     |                                 |        |

|         |                                 | PGood> |

| >VFB    | C865 (B_1_0)<br>PWM Singlephase | OVP>   |

| >ISENSE | DrMOS<br>Component1             | OCP>   |

| >IREF   |                                 | OTP>   |

|         |                                 | UVLO>  |

| >THWN   |                                 | DISB>  |

# **Product Detail**

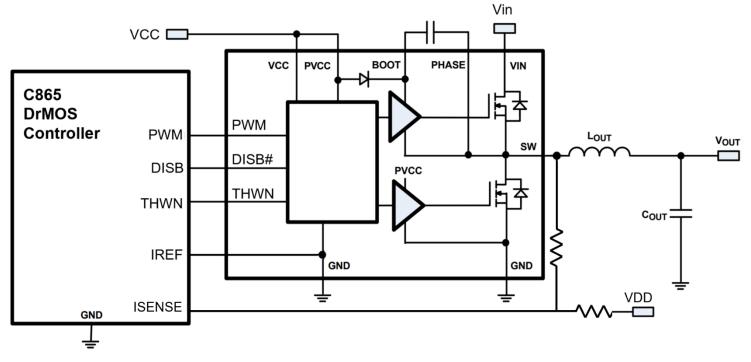

The C865\_B Synchronous Buck controller power component symbol is shown in Figure 1. The controller drives a DrMOS integrated power stage with connections as shown in Figure 2 and described in the Pin Function and Description Table. A typical application diagram is shown in Figure 3.

Output voltage feedback is compared against an internal reference using a high-performance voltage-error digitizer that provides tight voltage regulation accuracy under transient conditions. Pulse-width modulated (PWM), voltage-mode regulation is implemented with PID compensation. The switching frequency is either generated internally via an oscillator with selectable frequencies or provided via an external pin.

The customizable output voltage is specified by the power engineer during customization using AnDAPT's cloud-based WebAmp development software. The C865\_B component has customizable control and status pins including enable input, an optional power-good output, and optional output flags to signal when the system triggers an overvoltage (OVP), overcurrent (OCP), undervoltage lockout (UVLO), catastrophic failure or over temperature (OTP) condition. The threshold values are specified by the power engineer using the WebAmp tool.

Customizable soft-start and soft-stop slew rates are also specified by the power engineer using the WebAmp tool. Additional sequencing options are available when used in conjunction with the C420 Sequencer, by interconnecting signals EN and PGood to provide customizable dependencies and customizable delays between each sequence step.

\* R8 & R9 required on particular part numbers only

# Pin Function and Description Table

| Port<br>Name | NCP302035<br>NCP302040 | FDMF5820DC | AOZ5237QI<br>AOZ5339QI<br>AOZ5636QI | I/O | Description                                                                                                 |

|--------------|------------------------|------------|-------------------------------------|-----|-------------------------------------------------------------------------------------------------------------|

| EN           |                        |            |                                     | Ι   | Enable DrMOS controller                                                                                     |

| OVP          |                        |            |                                     | 0   | Over Voltage Protection fault flag for internal<br>connection to AmP fault manager                          |

| OCP          |                        |            |                                     | 0   | Over Current Protection fault flag for internal<br>connection to AmP fault manager                          |

| OTP          |                        |            |                                     | 0   | Over Temperature Protection fault flag for internal<br>connection to AmP fault manager                      |

| UVLO         |                        |            |                                     | 0   | Input Under Voltage Lock Out fault flag for internal<br>connection to AmP fault manager                     |

| PGood        |                        |            |                                     | 0   | Controller Power Good signal                                                                                |

| CFP          |                        |            |                                     | 0   | Catastrophic Fault Protection fault flag for internal connection to AmP fault manager.                      |

| VINFB        |                        |            |                                     | I   | Internal - Input voltage measurement for ViUVLO<br>protection                                               |

| PWM          | PWM                    | PWM        | PWM                                 | 0   | DrMOS power stage gate driver control signal<br>output from DrMOS controller                                |

| DISB         | DISB#                  | EN/FAULT#  | DISB#                               | 0   | Output disable pin. When this pin is pulled to a logic high level, the DrMOS Power Stage driver is enabled. |

| THWN         | THWN                   | TMON       | THWN                                | I   | Temperature monitor input from DrMOS Power Stage                                                            |

| ISENSE       |                        |            |                                     | Ι   | Current monitor input from DrMOS Power Stage                                                                |

| IREF         |                        |            |                                     | I   | Reference voltage connected to DrMOS power stage GND                                                        |

| VFB          |                        |            |                                     | Ι   | VOUT feedback for DrMOS controller                                                                          |

# **Electrical Characteristics**

PVIN= VIN=12V, TA=25°C, Cvdd=10µF, Cvcc=1µF, unless otherwise specified

| Parameters                                                                           | Test Conditions                                                                                                                                     | Min  | Тур | Max  | Units |

|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|-------|

| Output Voltage (Vout)                                                                |                                                                                                                                                     | 0.7  |     | 5.0  | V     |

| Output Voltage Regulation<br>(Vout)                                                  | Including load regulation and temperature variation V <sub>IN</sub> range: 4.5V to 14V                                                              | -1   |     | +1   | %     |

| Switching frequency (Fsw)                                                            |                                                                                                                                                     | 533  |     | 1000 | kHz   |

| Switching frequency accuracy                                                         |                                                                                                                                                     | -5   |     | +5   | %     |

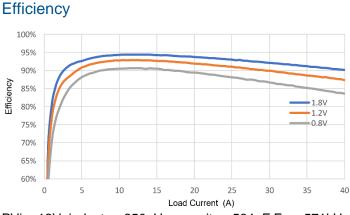

| Efficiency <sup>1</sup>                                                              | V <sub>IN</sub> =12V, V <sub>OUT</sub> =1.8V, F <sub>SW</sub> =571kHz,<br>I <sub>OUT</sub> =10A                                                     |      | 94  |      | %     |

|                                                                                      |                                                                                                                                                     |      |     |      |       |

| PROTECTION                                                                           |                                                                                                                                                     |      |     |      |       |

| ViUVLO, input Undervoltage<br>Lockout                                                |                                                                                                                                                     | 4    |     | 10   | V     |

| OCP, Over Current Protection<br>(% Іоит)                                             |                                                                                                                                                     |      | 150 |      | %     |

| OTP, Over Temperature<br>Protection for AmP device                                   | Shutdown (Power Good goes low)<br>Hysteresis                                                                                                        |      | 125 |      | °C    |

| OVP, Overvoltage Protection<br>trip point range<br>(relative to Vout Setting)        | No resistor divider on voltage<br>feedback. If a resistor divider is<br>used, these values will increase by a<br>factor equal to the divider ration | +100 |     | +432 | mV    |

| VoUVLO, output Undervoltage<br>Lockout threshold range<br>(relative to Vout Setting) | No resistor divider on voltage<br>feedback. If a resistor divider is<br>used, these values will increase by a<br>factor equal to the divider ration | -100 |     | -432 | mV    |

| Power Good threshold<br>(relative to Vout Setting)                                   | No resistor divider on voltage<br>feedback. If a resistor divider is<br>used, these values will increase by a<br>factor equal to the divider ratio  | -100 |     | -432 | mV    |

\* Parameters shaded in green are user customizable as set in WebAmP development software

<sup>1</sup> Efficiency measured with the AOZ5339 DrMOS

# **Digital GPIO Electrical Characteristics**

VIN=12V and TA=25°C

| I/O      | ١    | /ccio (V | )    |      | V <sub>IL</sub> (V) | VIH | (V)         | V <sub>OL</sub> (V) | V <sub>OH</sub> (V) | I <sub>OL</sub> | I <sub>ОН</sub> |

|----------|------|----------|------|------|---------------------|-----|-------------|---------------------|---------------------|-----------------|-----------------|

| Standard | Min  | Тур      | Max  | Min  | Max                 | Min | Max         | Max                 | Min                 | (mA)            | (mA)            |

| 3.3 V    | 3.14 | 3.3      | 3.46 | -0.3 | 0.8                 | 2.0 | Vccio + 0.2 | 0.4                 | Vccio – 0.5         | 2               | -2              |

# **Typical Characteristics**

Unless otherwise specified: TA = 25°C

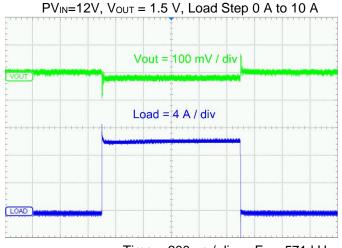

# **Transient Response**

$Time = 200 \ \mu s \ / \ div \qquad F_{sw} = 571 \ kHz$

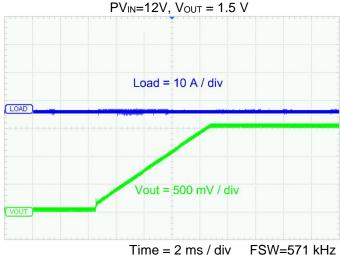

# Soft Start No Load

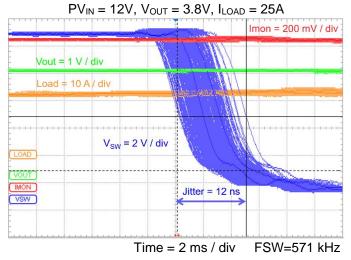

# **Jitter**

$PVin=12V,\ inductor=250nH,\ capacitor=564uF\ F_{SW}=571kHz$

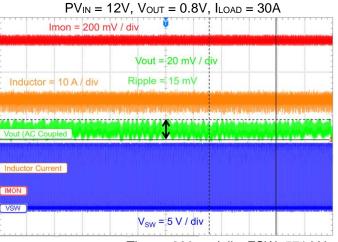

### **Ripple**

Time = 200  $\mu$ s / div FSW=571 kHz

# Theory of Operation

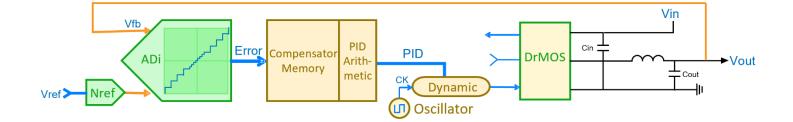

The C865\_B Synchronous Buck Regulator with integrated MOSFETs operates in voltage mode by comparing the  $V_{OUT}$  feedback voltage, Vfb, with a programmable reference, Vref to direct the PID (Proportional Integral Derivative) controller to produce a PWM (Pulse Width Modulation) input to the Hiside and Lo-side MOSFET switches as shown in Figure 4.

In CCM (Continuous Conduction Mode), the PWM driver goes high turning the Hi-side switch "ON" to provide  $\mathsf{PV}_{\mathsf{IN}}$  to

Figure 4: Functional Block Diagram

the LX side of an inductor, L, where  $V_L = V_{LX} - V_{OUT}$ . When the PWM driver goes low, the Hi-side switch turns "OFF", and after a shoot through delay, the Lo-side switch turns "ON" providing a path for the inductor current to decrease with  $V_L = -V_{OUT}$ , until the next PWM turns back "ON". As this cycle repeats, the PID algorithm regulates  $V_{OUT}$  by continuously updating the PWM cycle to optimize ripple, regulation, and transient response over changing load conditions.

### Start-up and Shutdown

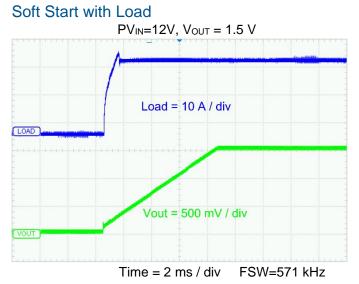

Start-up and shutdown are controlled by the EN digital port which may be connected to a GPIO pin or a control component such as the C420 Sequencer. When EN goes high, the output voltage, VOUT, will ramp up according to the Soft Start programmable preset ramp time in Parameter Settings. When EN goes low, the output voltage, VOUT, will ramp down according to the Soft Start programmable preset ramp time in Parameter Settings.

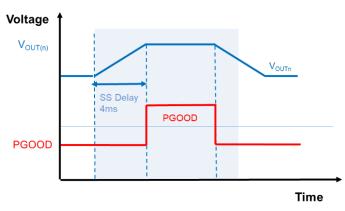

### PGood

The power-good, PGood, digital port may be connected to a GPIO pin or a control component such as the C420 Sequencer to indicate the output voltage regulation status. PGOOD goes high on power-up after completion of all the Soft Start time (Figure 5) and when all Faults are cleared. PGOOD will go low for faults such as ViUVLO, VoUVLO, OVP over voltage, OCP current limit, or OTP thermal shutdown. PGOOD will also go low if EN goes low.

Figure 5 Soft Start PGOOD wavforms

# **Protection Features**

The C865\_B provides many protection features including ViUVLO, OVP, OCP and OTP.

# ViUVLO

The PV<sub>IN</sub> voltage Under Voltage Lockout, ViUVLO, digital port may be connected to a GPIO pin or a control component such as Digital Logic Block to indicate the PV<sub>IN</sub> voltage status. ViUVLO flag stays low when PV<sub>IN</sub> voltage is higher than the programmable preset condition in Parameter Settings. ViUVLO goes high when PV<sub>IN</sub> voltage is less than the programmable preset condition in Parameter Settings. PVIN may be sensed on the GPIO pin connected to the PVINFB analog port which is resistor divided by a fixed 1/6 ratio of PVIN. On detection of ViUVLO, the C865\_B will power down and PGood will go low. On ViUVLO returning low, the C865\_B will restart with a new Soft Start cycle.

# ViUVLO from Power Stage (DrMOS)

In addition to the standard protections which are implemented at the device level using other power components, the C865\_B also includes other protection depending on the DrMOS used.

### OVP

The Over Voltage Protection, OVP, digital port may be connected to a GPIO pin or control component logic blocks

to indicate the output voltage over voltage status. OVP goes high when output voltage,  $V_{OUT}$ , is higher than the programmable preset condition in Parameter Settings. OVP goes low when output voltage,  $V_{OUT}$ , is less than the programmable preset condition in Parameter Settings. On detection of OVP, the C865\_B will skip Hi-side switch pulses until OVP returns low.

# OCP

The Over Current Protection, OCP, digital port may be connected to a GPIO pin or control component logic blocks to indicate the output over current status. When  $I_{OUT}$ , is greater than 150% of the Output Current setting, the C865\_B will shutdown. The user needs to toggle EN down and then UP to restart the controller.

# OTP

Thermal shutdown is provided to protect the regulator from excessive junction temperature. When the junction temperature reaches 125°C the device shuts down. On detection of OTP, the C865\_B will power down and PGood will go low. On OTP returning low, an EN cycling low-to-high, will restart the C865\_B with a new Soft Start cycle.

# **Parameter Settings**

# **Basic Configuration**

Default parameters may be changed per user requirement.

| SW FreqCK0 0.8 MHz 0°PVIN Voltage12VPVin NamePVin1Output Voltage1.2VVout NameVout1VVout Ripple0.62%Vout Overshoot0.01VOutput Current30AIout Ripple30%                                             | <ul> <li>Basic Configu</li> </ul> | iration ——    |   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------|---|

| PVin Name     PVin1       Output Voltage     1.2     V       Vout Name     Vout1     Vout1       Vout Ripple     0.62     %       Vout Overshoot     0.01     V       Output Current     30     A | SW Freq                           | CK0 0.8 MHz 0 | • |

| Output Voltage     1.2     V       Vout Name     Vout1       Vout Ripple     0.62     %       Vout Overshoot     0.01     V       Output Current     30     A                                     | PVIN Voltage                      | 12            | v |

| Vout Name     Vout1       Vout Ripple     0.62     %       Vout Overshoot     0.01     V       Output Current     30     A                                                                        | PVin Name                         | PVin1         |   |

| Vout Ripple     0.62     %       Vout Overshoot     0.01     V       Output Current     30     A                                                                                                  | Output Voltage                    | 1.2           | V |

| Vout Overshoot     0.01     V       Output Current     30     A                                                                                                                                   | Vout Name                         | Vout1         |   |

| Output Current 30 A                                                                                                                                                                               | Vout Ripple                       | 0.62          | % |

|                                                                                                                                                                                                   | Vout Overshoot                    | 0.01          | V |

| Iout Ripple 30 %                                                                                                                                                                                  | Output Current                    | 30            | А |

|                                                                                                                                                                                                   | lout Ripple                       | 30            | % |

| lout Delta 10 A                                                                                                                                                                                   | lout Delta                        | 10            | А |

Vour ripple is computed as follows:

Vour ripple = Iripple/(8\*Cour\*Fsw)

# **DrMOS Selection**

The following DrMOS devices require two 10 k $\Omega$  pulldown resistors, as shown in Figure 2, because they have very high input impedances on their PWM and DISB# inputs:

- onsemi NCP302035

- onsemi NCP302040

- onsemi NCP302150

- Alpha & Omega Semiconductor AOZ5237QI

Choose the DrMOS device from the pull-down menu below:

| DrMOS              |                                                              |   |  |  |  |

|--------------------|--------------------------------------------------------------|---|--|--|--|

| DrMOS Chip ①       | On Semi NCP302035                                            | ~ |  |  |  |

|                    | On Semi NCP302035                                            |   |  |  |  |

| LC Components      | On Semi NCP302040<br>On Semi NCP302150<br>On Semi FDMF5820DC |   |  |  |  |

| │ □Manual Set LC Φ | AOS AOZ5339QI<br>AOS AOZ5636QI<br>AOS AOZ5237QI              |   |  |  |  |

# LC Component Selection

Default values for Inductance, L, and output capacitance, Cout, are computed as follows:

$L = (V_{IN}-V_{OUT})^* V_{OUT} / (V_{IN} *Fsw*Iripple)$

C<sub>OUT</sub> = I<sub>OUT</sub>delta<sup>2\*</sup>L / (2\* V<sub>OUT</sub> \*Vos)

| Manual Set LC   |      |     |  |  |  |

|-----------------|------|-----|--|--|--|

| Inductor        | 0.15 | μH  |  |  |  |

| Inductor DCR    | 10   | mΩ  |  |  |  |

| Capacitor       | 625  | μF  |  |  |  |

| Cap ESR         | 4    | mΩ  |  |  |  |

| f <sub>LC</sub> | 16.4 | kHz |  |  |  |

Inductor and Capacitor values may be changed by checking Manual Set LC or selecting the BoM tab where manufacturers part numbers may be selected.

# Vfb Resistor Components

Feedback divider resistors R1 and R2 default to 49.9  $\Omega$  and open (infinity). When V<sub>OUT</sub> is larger than 2.25V, a resistor divider ratio is computed to select 1% resistor values for both R1 and R2.

| Manual Set R | esistors — |    |

|--------------|------------|----|

| R1           | 0.0499     | kΩ |

| R2           | Infinity   | kΩ |

| Vfb          | 1.2        | v  |

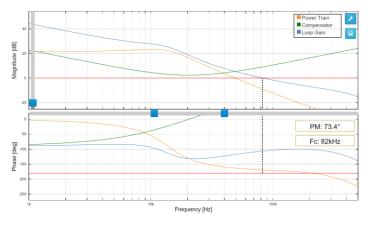

# Controller

The controller compensation memory block provides PID compensation of error signals using the integrated compensation logic without external passives or an arithmetic unit. The user can adjust a bandwidth, a gain, and a phase margin of the compensation logic. For example, a user can interactively adjust the proportional gain Kp and the gains Fz1 and Fz2 shown below to effectively adjust the derivative and integral gains Kd and Ki as well as the bandwidth and the phase margin.

| – Controller –  |             |     |

|-----------------|-------------|-----|

| Gain            | 400         |     |

| F <sub>z1</sub> | 8           | kHz |

| F <sub>z2</sub> | 32          | kHz |

| Ki              | 2.010619e+7 |     |

| Kd              | 1.989437e-3 |     |

|                 |             |     |

Gain, Fz1 and Fz2 are chosen to provide best Phase Margin and Crossover Frequency, Fc, as adjusted in the Bode Plot shown below:

### **Fault Protection**

Input voltage Under Voltage Lockout, ViUVLO, indicates the input voltage status greater or less than programmable preset condition (default 4.5V). Output voltage Under Voltage Lockout, VoUVLO, indicates the output voltage status greater or less than programmable preset condition (default 75% of Vout). Over Voltage Protection, OVP, indicates output voltage status greater or less than the programmable preset condition (default 25% above Vout). Over Current Protection, OCP, indicates the output over current greater or less than the programmable preset condition. Over Temperature Protection, OTP, indicates thermal shutdown has occurred. (set to 125°C)..

| Fault Protection |                  |   |  |  |

|------------------|------------------|---|--|--|

| Enable Input     | UVLO             |   |  |  |

| Input UVLO       | 5                | V |  |  |

| Output UVLO      |                  |   |  |  |

| Output UVLO      | 0.9              | V |  |  |

| Cycle by cycl    | le current limit |   |  |  |

| OCP Level        | 45               | А |  |  |

| ✓Enable OVP      |                  |   |  |  |

| OVP Level        | 1.5              | V |  |  |

| Enable OTP       |                  |   |  |  |

| Over Temperature | 125              |   |  |  |

| OTP Shutdown     |                  |   |  |  |

| OTP Hiccup       |                  |   |  |  |

### Fault Protection Power Stage

In addition to the standard protection which are implemented at the device level using other power components, the C865\_B also includes other protection depending on the DrMOS used. When Hiccup options are selected, then the controller will shut down and automatically power up when the power stage fault has cleared.

# Power Stage Fault Protection Input UVLO UVLO Shutdown UVLO Hiccup Over Current OCP Shutdown OCP Hiccup Over Temperature OTP Shutdown OTP Hiccup

### Constraints

Soft Start times of 1 to 16 milliseconds are programmable by the user as a parameter selection. The default is 8 milliseconds as shown. Power Good ranges 59% to 100% and default is 85%.

| Constraints – |    |    |

|---------------|----|----|

| Soft Start —  |    |    |

| Rise Time     | 8  | ms |

| ✓Power Good   |    |    |

| Power Good    | 85 | %  |

|               |    |    |

### Additional Information DrMOS

For additional information see DrMOS supplier datasheets such as onsemi NCP302035/2040/2150/FDMF5820DC and Alpha & Omega Semiconductor AOZ5339QI/5636QI/5237QI DrMOS recommended for use with C865\_B.

# C865\_B Resource Usage

```

Circuit Stats...

Number of AnD Temp_Sensor

1

Number of AnD ADi dual

1

Number of AnD ATC IO

8

Number of AnD ATC Comp

4

Number of AnD ATC Summer

1

3

Number of AnD PMT

Number of AnD CM PID

2

Number of AnD Nref dyn

1

Number of AnD Nref fix

4

Number of AnD PTG Phase Count 1

Number of AnD_PTG_GBUF

1

Number of AnD PTG OSC

1

Number of AnD DFFN

11

Number of AnD DFF

29

Number of LUT4

104

Resource Usage...

8 used (Capacity 24)

io

clb

14 used (Capacity 64)

2 used (Capacity 8)

сm

3 used (Capacity 16)

pmt

atc

6)

3 used (Capacity

corner 3 used (Capacity

4)

1 used (Capacity

2)

ptg

uLogic 104 used (Capacity 512)

Components Stats...

$techmap\component 1

AnD DFF

26

AnD DFFN

4

$techmap\otp fuse module

AnD DFF

3

7

AnD DFFN

component 1

AnD ADi dual

1

AnD ATC Comp

3

AnD ATC Summer

1

AnD CM PID

2

AnD Nref dyn

1

3

AnD Nref fix

AnD PMT

3

otp fuse module

AnD ATC Comp

1

AnD Nref fix

1

```

10

# Internal PMIC Blocks and Resources

Each Power Component uses several blocks and resources that are available as part of the AmP platform. Listed below is a description of blocks and resources that are used to create C865\_B power components. An example application is shown in Figure 12.

### Noise-immune references - Nrefs

- 10 bit, 0.1% resolution for <0.5% regulation

- Curvature compensated band-gap trim

- Precision across process, temperature

Nrefs provide reference voltages to analog GPIOs, Adaptive Digitizers, Threshold Comparators, In Amp, SIM linear LDO and SIM protect. On power-up, Nrefs are configured to voltages specified by the user.

# Compensator Memory – CRAM

- Flexible, high bandwidth PID

- Adjust gain/phase margin, bandwidth

- Symmetric, binary scaling cuts memory by four

- Adaptive, dual regulation, 1 or 2 pole

The CRAM provides digital compensation to integrated MOSFETs implementing switching regulator functions including buck, boost and multi-phase regulators. The CRAM implements the Proportional Integral Derivative algorithm, PID, as in the following equation:

$$\begin{split} \mathsf{P}[\mathsf{n}] &= \mathsf{P}[\mathsf{n}\text{-}1]^*\mathsf{a}1 + \mathsf{P}[\mathsf{n}\text{-}2]^*\mathsf{a}2 + \mathsf{E}[\mathsf{n}]^*\mathsf{a} + \mathsf{E}[\mathsf{n}\text{-}1]^*\mathsf{b} + \mathsf{E}[\mathsf{n}\text{-}2]^*\mathsf{c} \\ 1 \text{ pole: } \mathsf{a}1 &= \mathsf{1}, \quad \mathsf{a}2 &= \mathsf{0} \quad 2 \text{ pole: } \mathsf{a}1 &= \mathsf{0.5}, \, \mathsf{a}2 &= \mathsf{0.5} \\ \mathsf{E}[\mathsf{n}] &= \mathsf{Vref}\text{-}\mathsf{Vout}[\mathsf{n}] \end{split}$$

# Precision Modulation Timers - PMTs

- 11-bit, 1.25 ns resolution

- Static, dynamic or stopwatch

- Lowers bias current, system freq.

The PMT provides precision delays for Pulse Width Modulation (PWM), MOSFET turn-on, turn-off timing and sensor sample timing. Delays may be fixed or dynamic ranging from nanoseconds, milliseconds, microseconds to seconds with resolution less than one nanosecond.

### Adaptive Digitizer – ADi

- Digitize feedback Error

- Highest precision at reference point

- Low cost & fast sampling

The ADi converts differential analog signals from GPIOs or Nrefs and deliver up to 10-bits digital signed magnitude numbers to the digital fabric. Each ADi consists of two digitizers to provide highest speed and precision.

Figure 12: AmP Blocks and Resources driving DrMOS Example - Buck Regulator

# **Additional Resources**

<u>AnDAPT AmP Platform\_B datasheet</u>

# **Revision History**

| Date       | Revision                                                                                                                             |

|------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 12/17/2022 | Adjustable output voltage with down to 2.4 mV resolution changed to 2.5 mV resolution When VOUT is larger than 2.3V changed to 2.25V |

| 04/07/2022 | Added $10k\Omega$ R8 and $10k\Omega$ R9, Figure 2: DrMOS Interface. Added onsemi NCP302150                                           |

| 04/11/2021 | Added 1k $\Omega$ R6 and 10k $\Omega$ R7, Figure 2: DrMOS Interface.                                                                 |

| 08/17/2020 | Preliminary release                                                                                                                  |

# AnDAPT On-Demand Power Management

www.AnDAPT.com

### Trademarks

© 2022 AnDAPT, LLC, the AnDAPT logo, AmP, WebAmP, AmPLink, AmPScope, WebAdapter and other designated brands included herein are trademarks of AnDAPT, LLC in the United States and other countries. All other trademarks are the property of their respective owners.

12