全面的电源管理

全面的电源管理

电源树映射 – 全面的电源管理

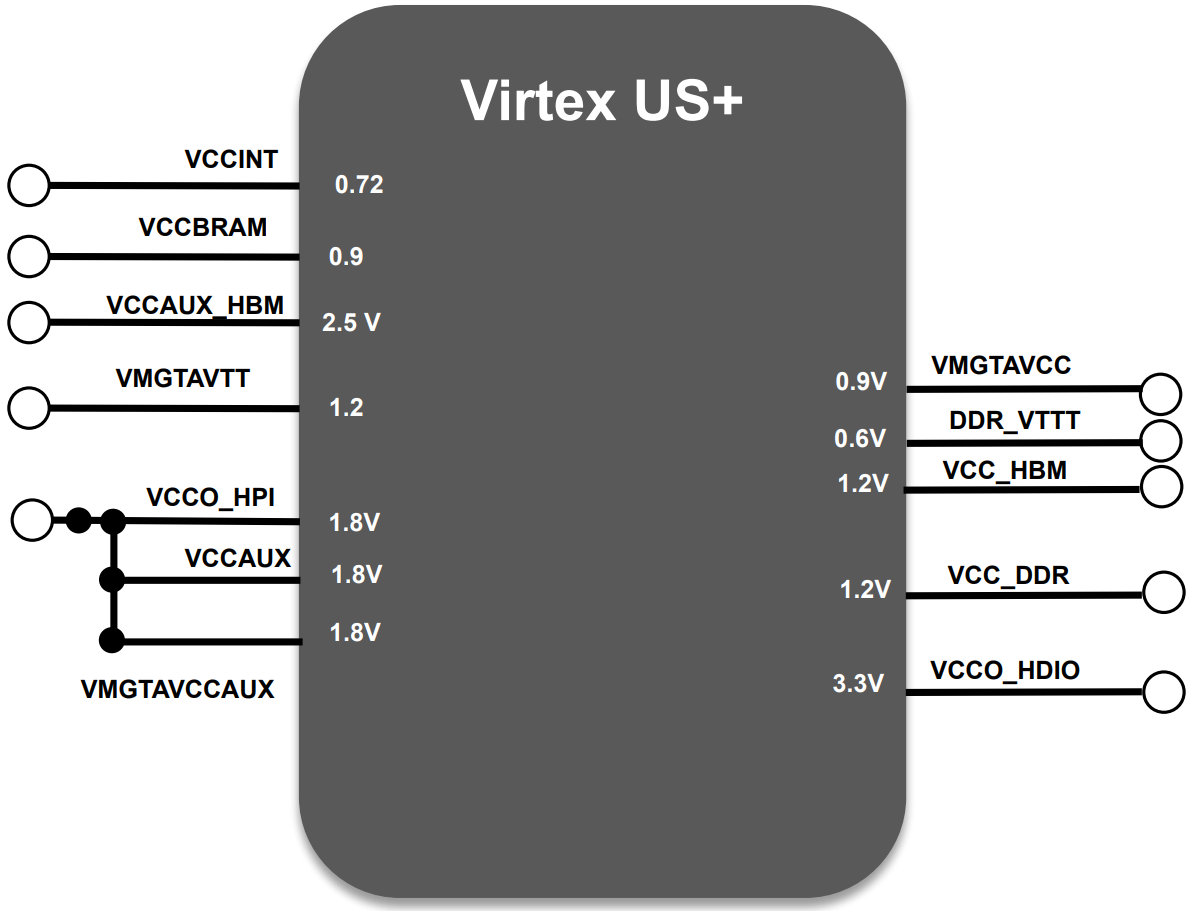

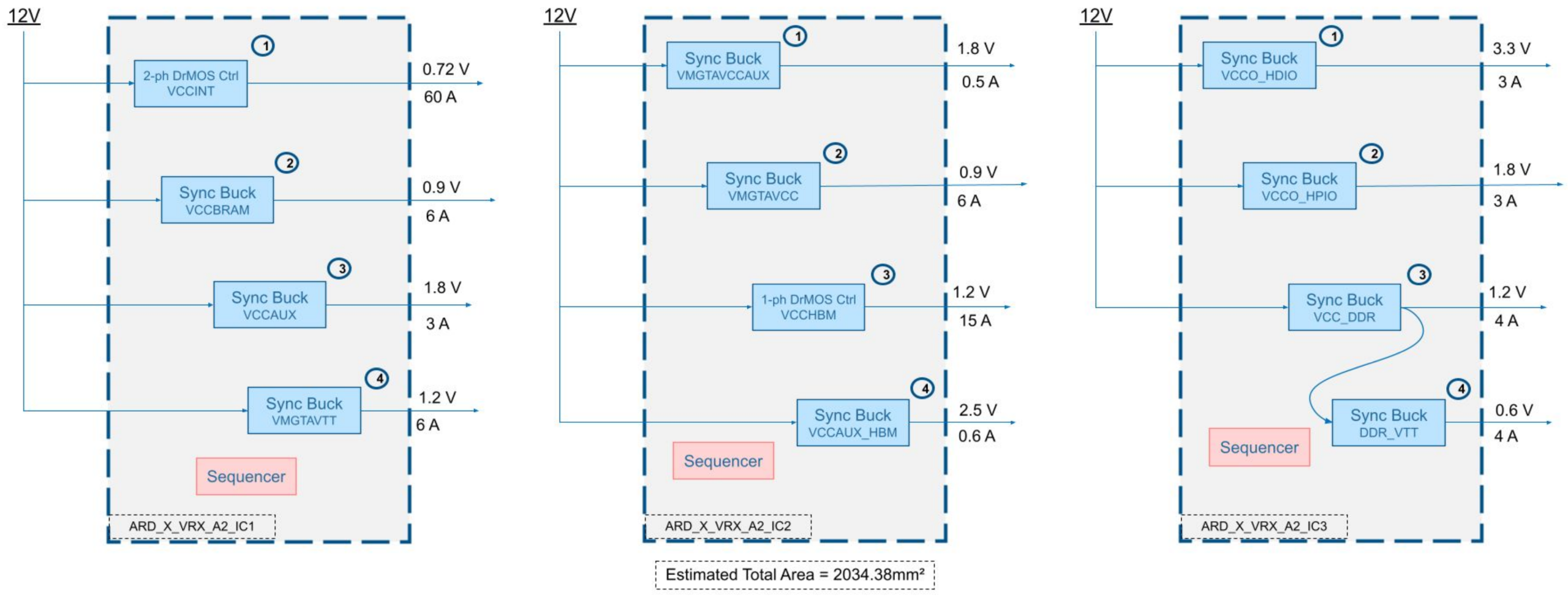

| # | 轨 | 电子表格列 柱子 | 顺序 | 电源组件 | 类型 | 上游铁路 | 输入电压(V) | 输出电压 (V) | 电流输出 (A) | AnDAPT PMIC |

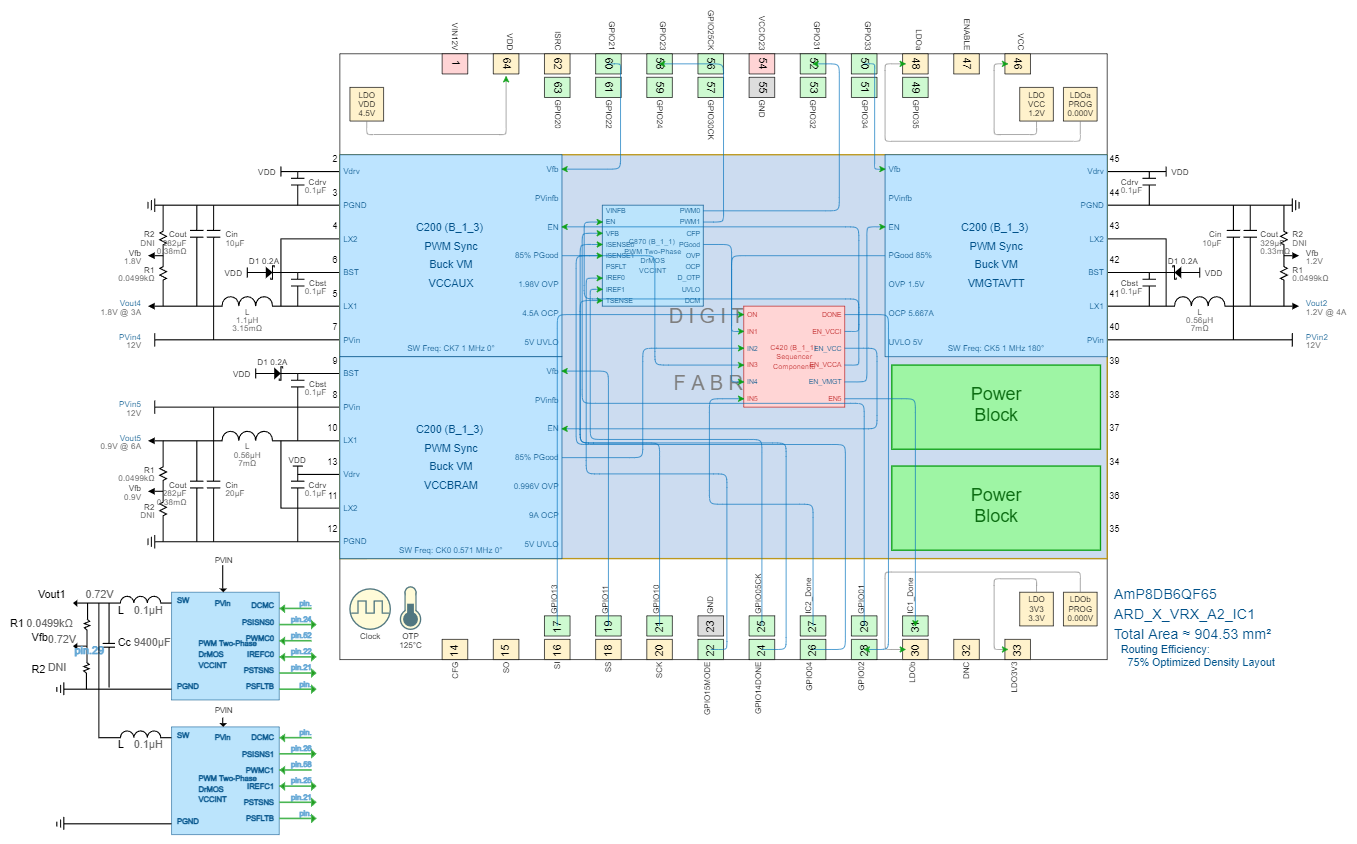

| 1 | VCCINT | 12 | 1 | C870 | 2-ph DrMOS Ctrl | PVIN | 12 | 0.72 | 60 | ARD_X_VRX_A2_IC1 |

| 2 | VCCBRAM (VCCINT_IO, VCCBRAM) | 3 | 2 | C200 | 同步降压 | PVIN | 12 | 0.9 | 6 | ARD_X_VRX_A2_IC1 |

| 3 | VCCAUX (VCCAUX, VCCAUX_IO, VCCADC) | 1 | 3 | C200 | 同步降压 | PVIN | 12 | 1.8 | 3 | ARD_X_VRX_A2_IC1 |

| 4 | VMGTAVTT | 7 | 4 | C200 | 同步降压 | PVIN | 12 | 1.2 | 6 | ARD_X_VRX_A2_IC1 |

| 5 | VMGTAVCCAUX | 2 | 5 | C200 | 同步降压 | PVIN | 12 | 1.8 | 0.5 | ARD_X_VRX_A2_IC2 |

| 6 | VMGTAVCC | 3 | 6 | C200 | 同步降压 | PVIN | 12 | 0.9 | 6 | ARD_X_VRX_A2_IC2 |

| 7 | VCC_HBM (VCC_HBM, VCC_IO_HBM) | 10 | 7 | C865 | 1-ph DrMOS Ctrl | PVIN | 12 | 1.2 | 15 | ARD_X_VRX_A2_IC2 |

| 8 | VCCAUX_HBM | 4 | 8 | C200 | 同步降压 | PVIN | 12 | 2.5 | 0.6 | ARD_X_VRX_A2_IC2 |

| 9 | VCCO_HDIO | 5 | 9 | C200 | 同步降压 | PVIN | 12 | 3.3 | 3 | ARD_X_VRX_A2_IC3 |

| 10 | VCCO_HPIO | 6 | 10 | C200 | 同步降压 | PVIN | 12 | 1.8 | 3 | ARD_X_VRX_A2_IC3 |

| 11 | VCC_DDR | 7 | 11 | C200 | 同步降压 | PVIN | 12 | 1.2 | 4 | ARD_X_VRX_A2_IC3 |

| 12 | DDR_VTT (DDR_VTT, DRR_VREF) | 8 | 12 | C210 | VTT 终结者 | VCC_DDR | 1.2 | 0.6 | 4 | ARD_X_VRX_A2_IC3 |

ANDAPT 解决方案 – 全面的电源管理

设计视图 IC1

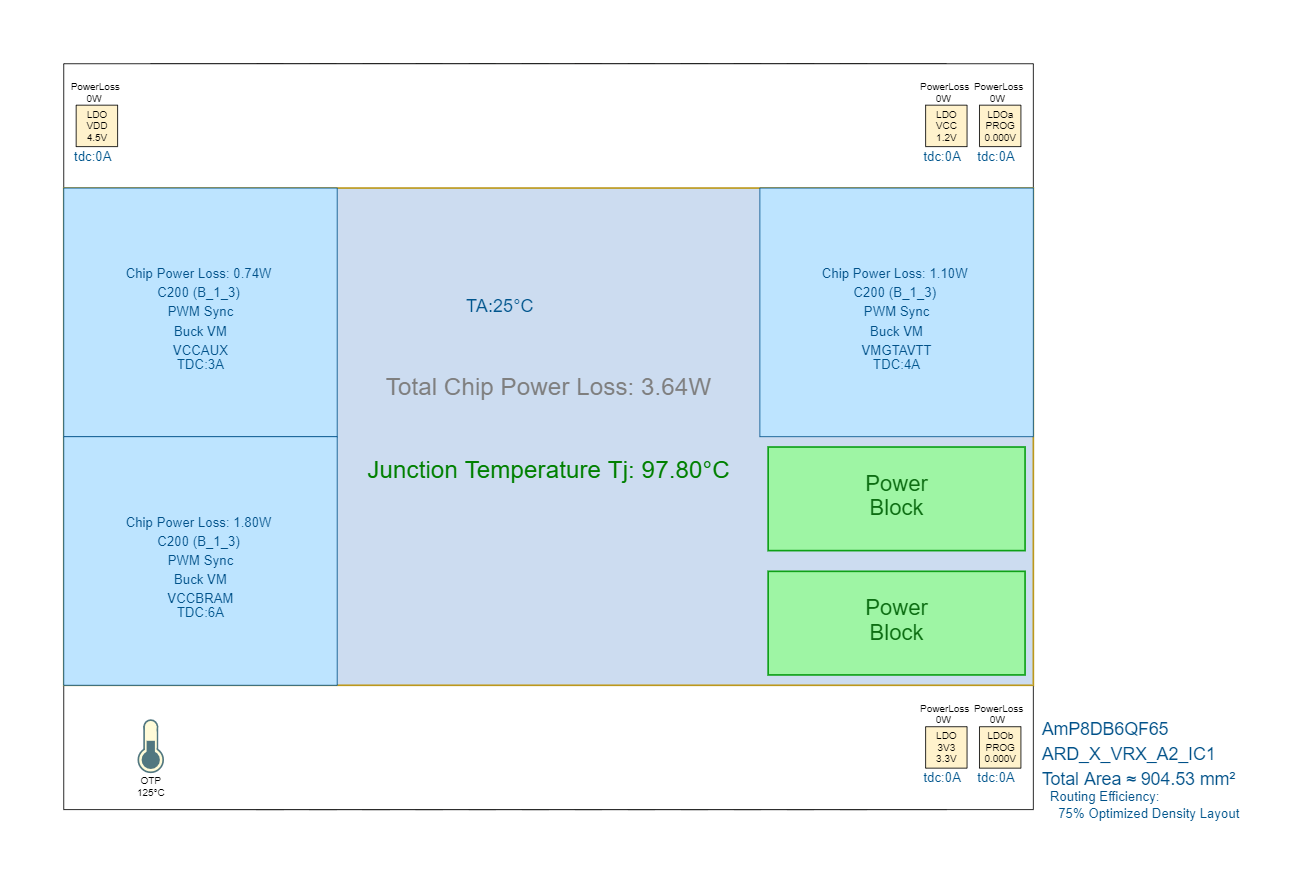

热视图 IC1

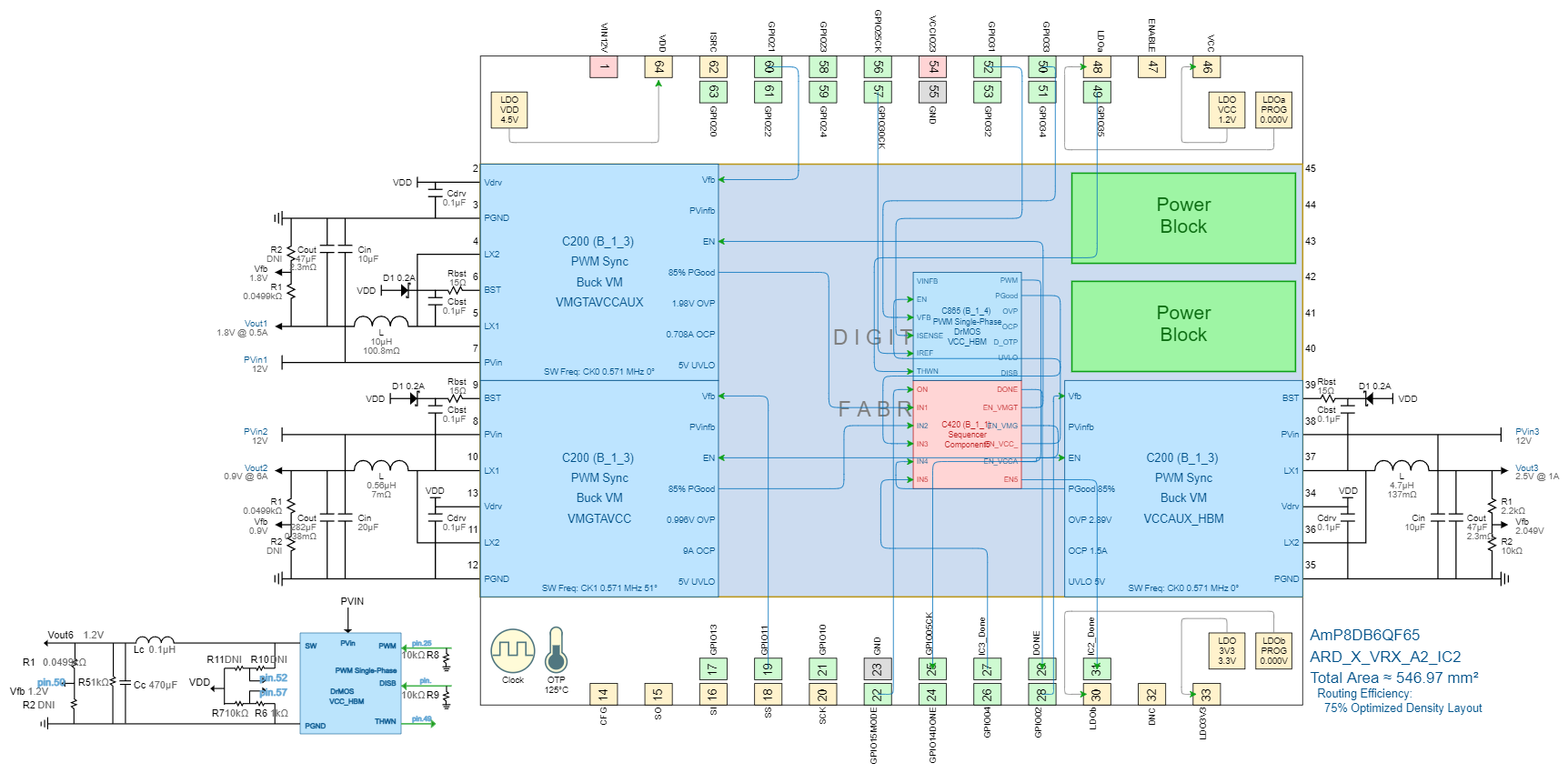

设计视图 IC2

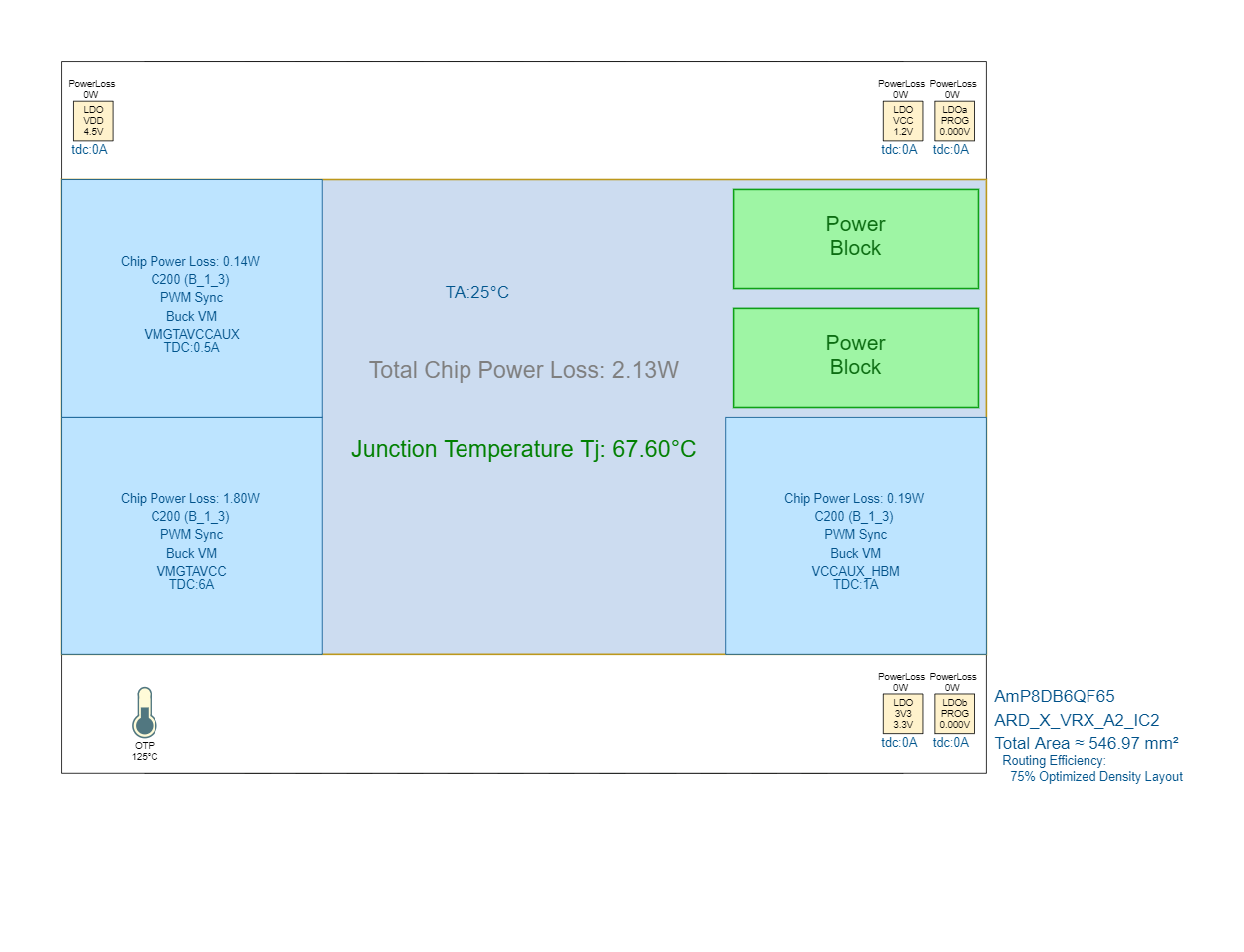

热视图 IC2

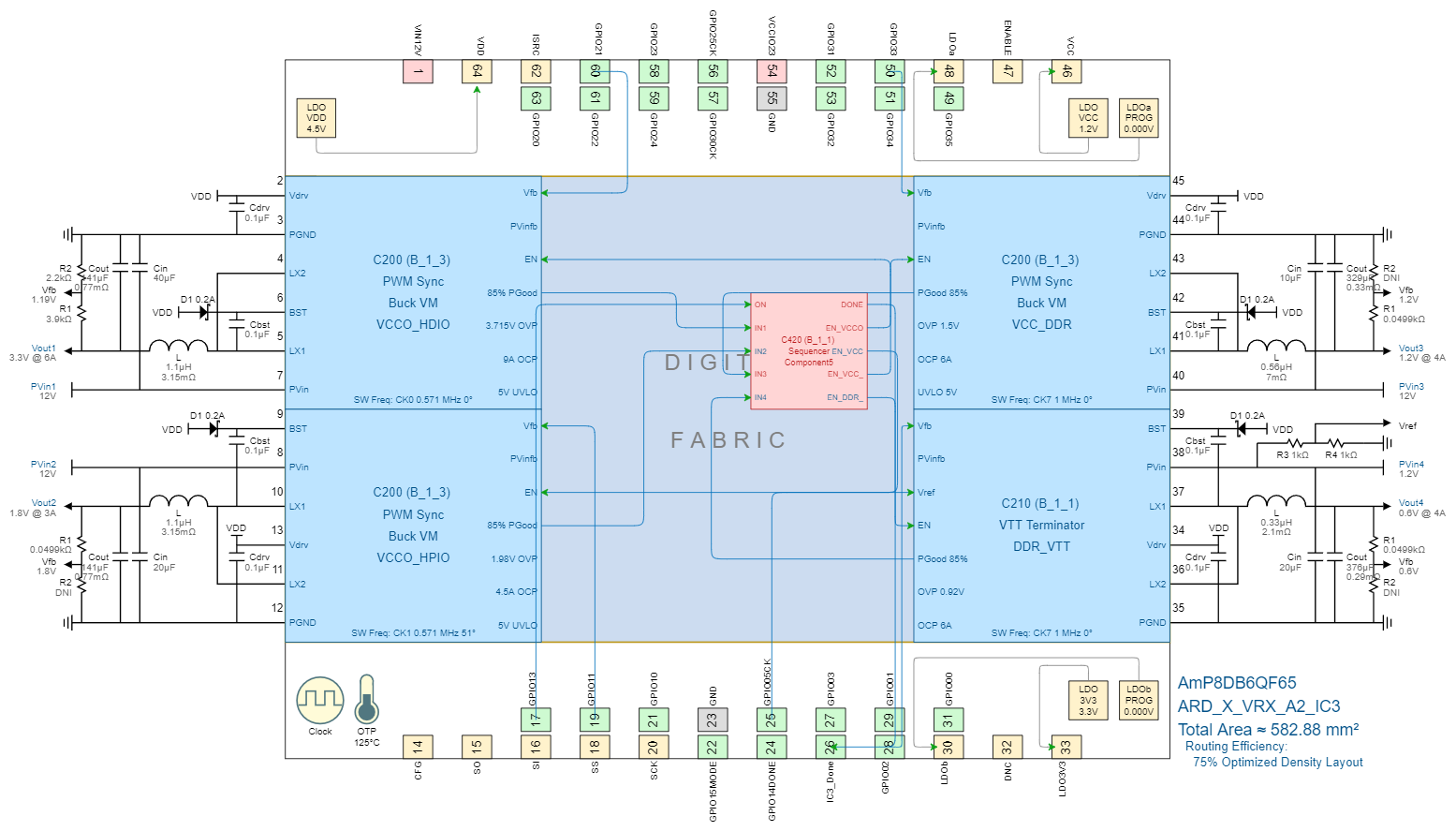

设计视图 IC3

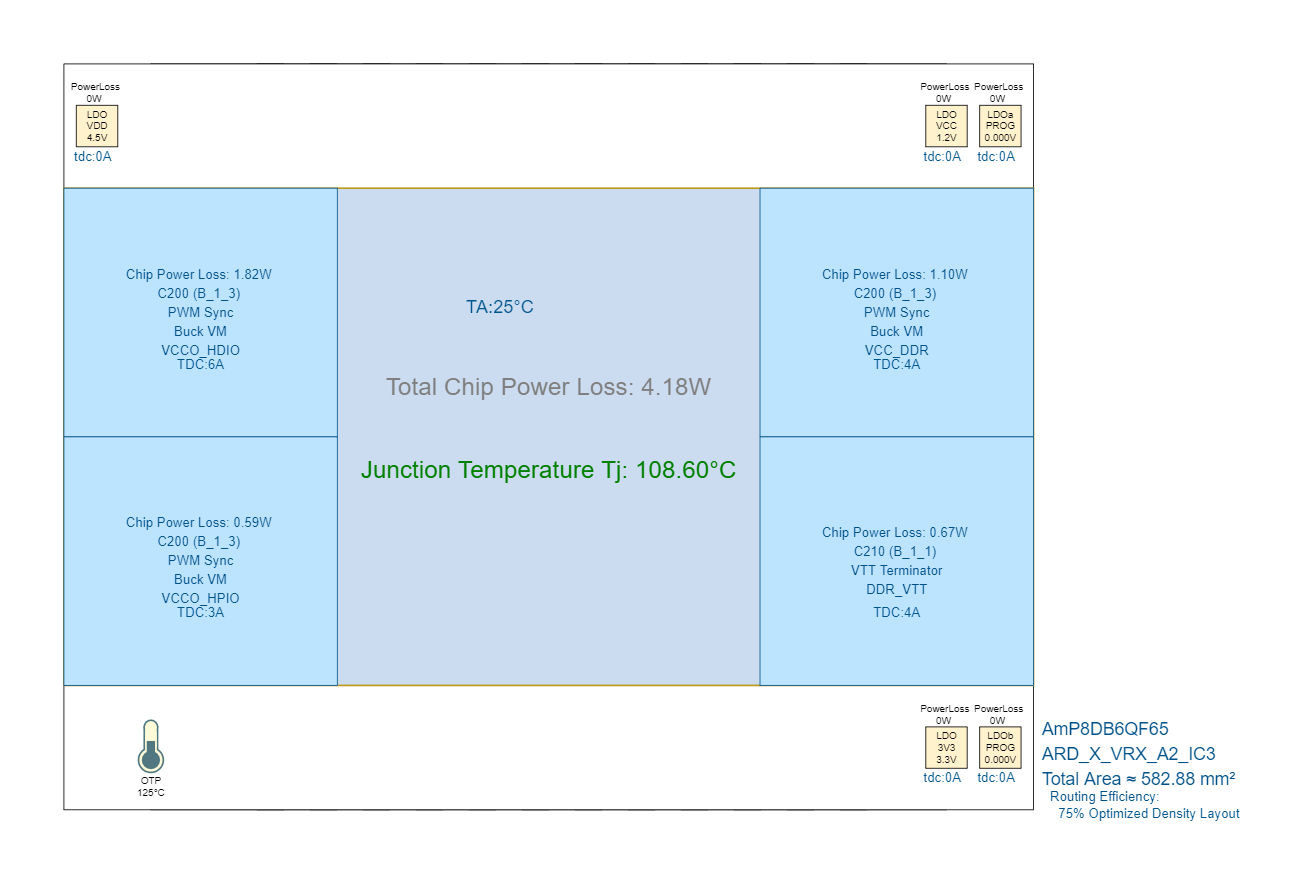

热视图 IC3