Mandatory Power

功率树映射 – 强制功率域

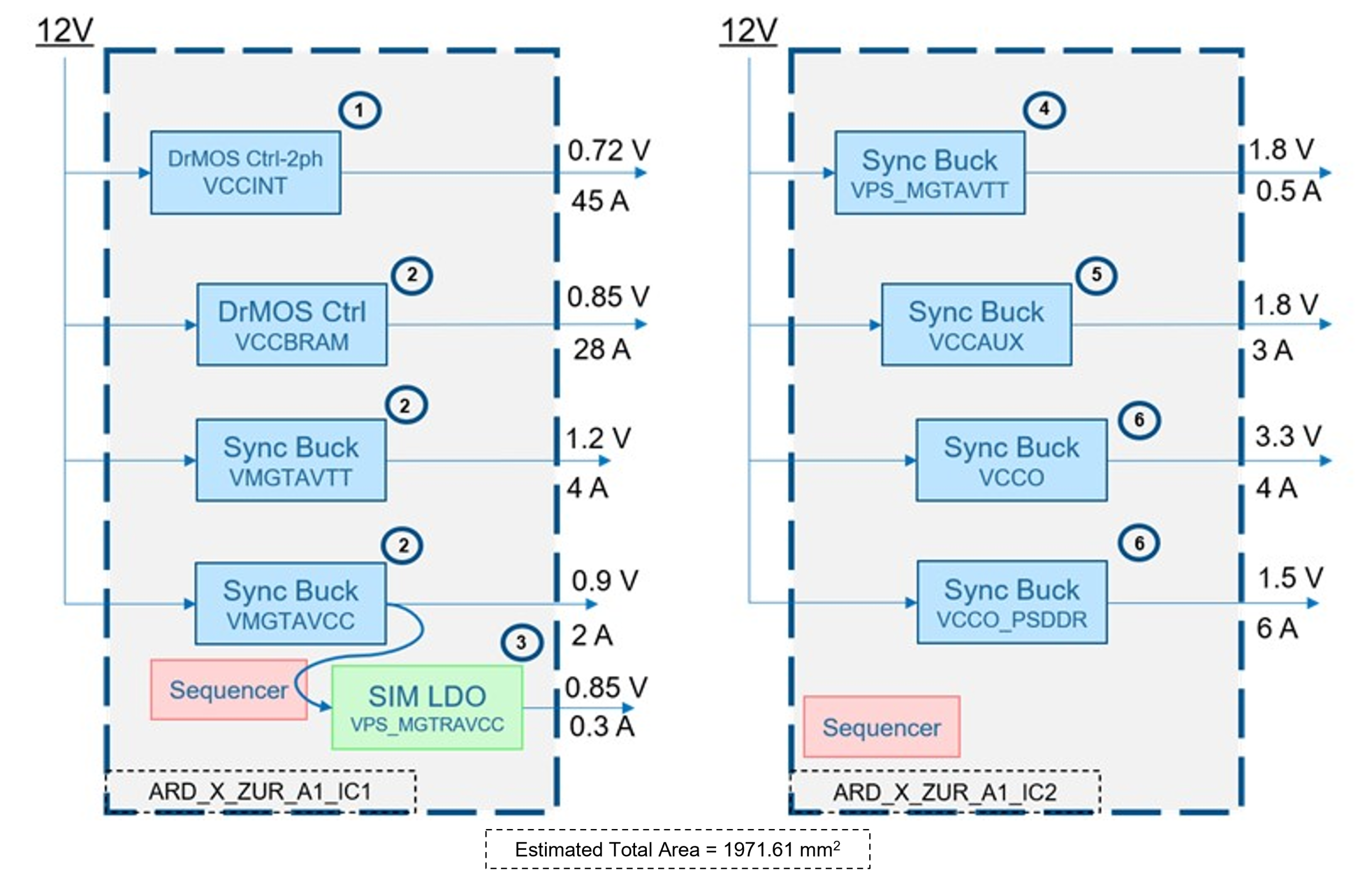

| # | 轨 | 顺序 | 电源组件 | 类型 | 上游铁路 | 输入电压(V) | 输出电压 (V) | 电流输出 (A) | AnDAPT PMIC |

| 1 | VCCINT | 1 | C870 | DrMOS Ctrl 2-ph | VIN | 12 | 0.72 / 0.85 | 45 | ARD_X_ZUR_A1_IC1 |

| 2 | VCCBRAM, INT_IO, INT_AMS, SDFEX | 2 | C860 | DrMOS Ctrl 1-ph | VIN | 12 | 0.85 | 28 | ARD_X_ZUR_A1_IC1 |

| 3 | VMGTAVTT, VCC_PSPLL, VCCU_PLL | 2 | C200 | 同步降压 | VIN | 12 | 1.2 | 4 | ARD_X_ZUR_A1_IC1 |

| 4 | MGTAVCC | 2 | C200 | 同步降压 | VIN | 12 | 0.9 | 2 | ARD_X_ZUR_A1_IC1 |

| 5 | VPS_MGTRAVCC | 3 | C710 | SIM LDO | MGTAVCC | 0.9 | 0.85 | 0.3 | ARD_X_ZUR_A1_IC1 |

| 6 | VCCO_PSDDR, DDR_VDDQ | 6 | C200 | 同步降压 | VIN | 12 | 1.1 – 1.5 | 6 | ARD_X_ZUR_A1_IC2 |

| 7 | VCCAUX, ADC, IO, VCCPSAUX, DDR_PLL, ADC | 5 | C200 | 同步降压 | VIN | 12 | 1.8 | 2 – 3 | ARD_X_ZUR_A1_IC2 |

| 8 | VCCO | 6 | C200 | 同步降压 | VIN | 12 | 3.3 / 5 | 4 | ARD_X_ZUR_A1_IC2 |

| 9 | VPS_MGTAVTT, VMGTVAUX | 4 | C200 | 同步降压 | VIN | 12 | 1.8 | 0.5 | ARD_X_ZUR_A1_IC2 |

ANDAPT 解决方案 – 强制功率域

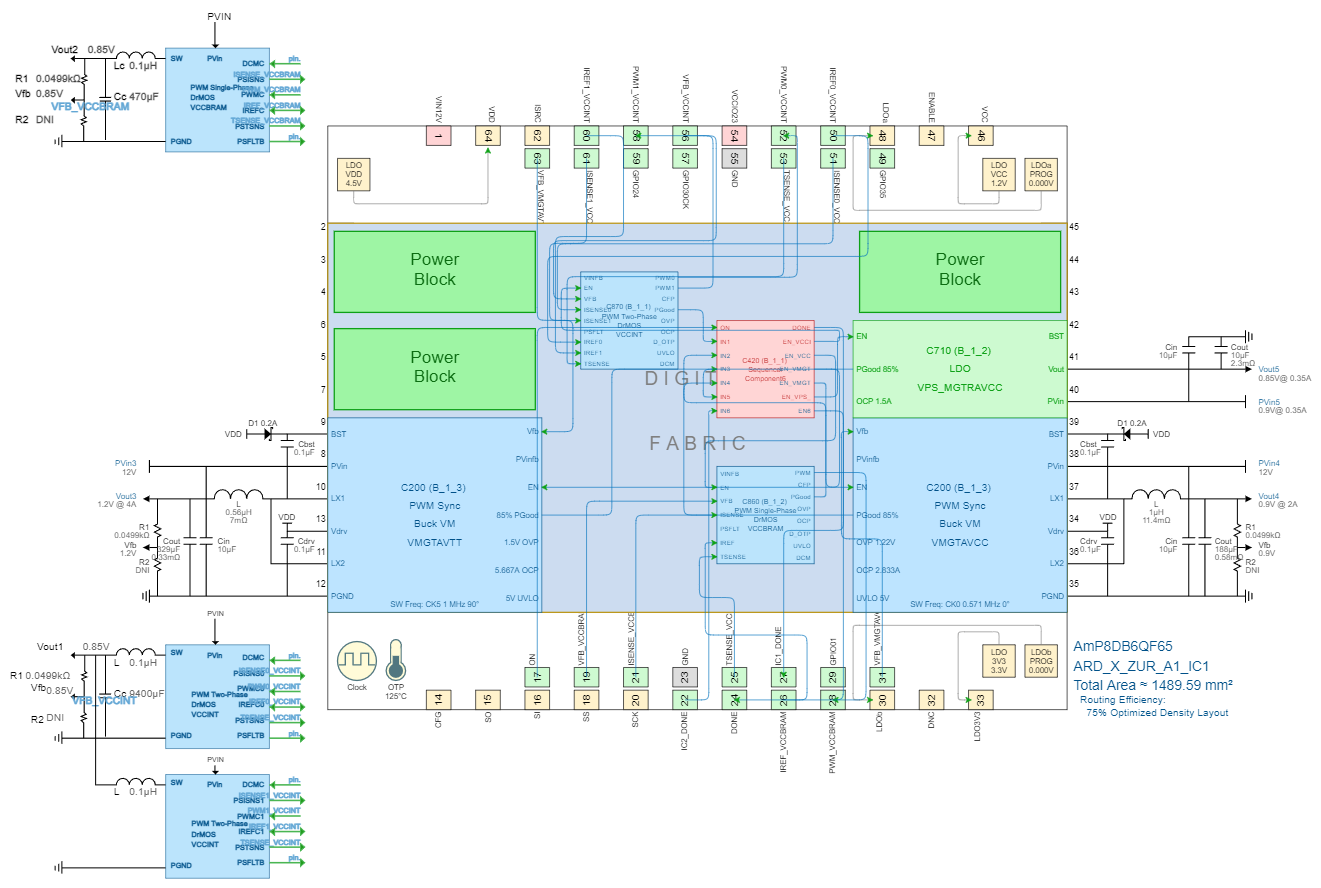

设计视图 IC1

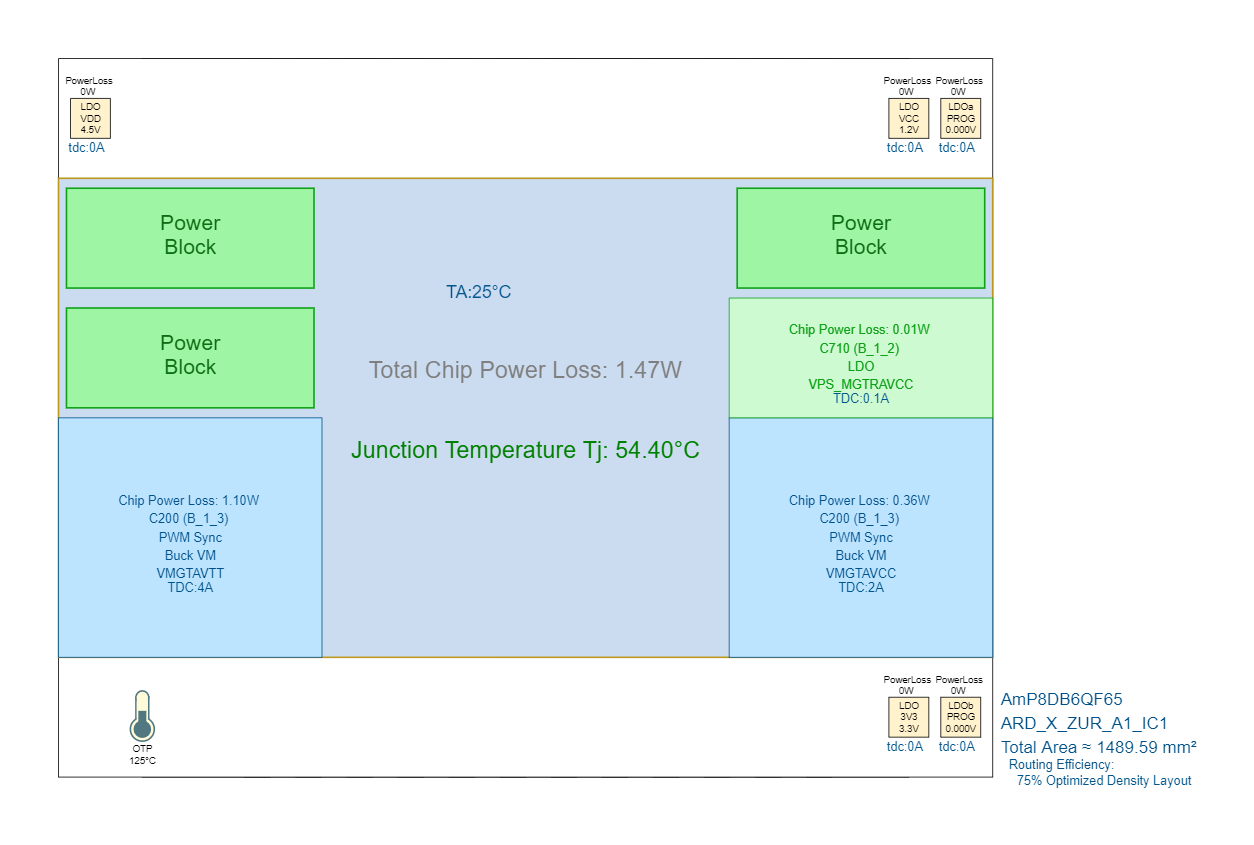

热视图 IC1

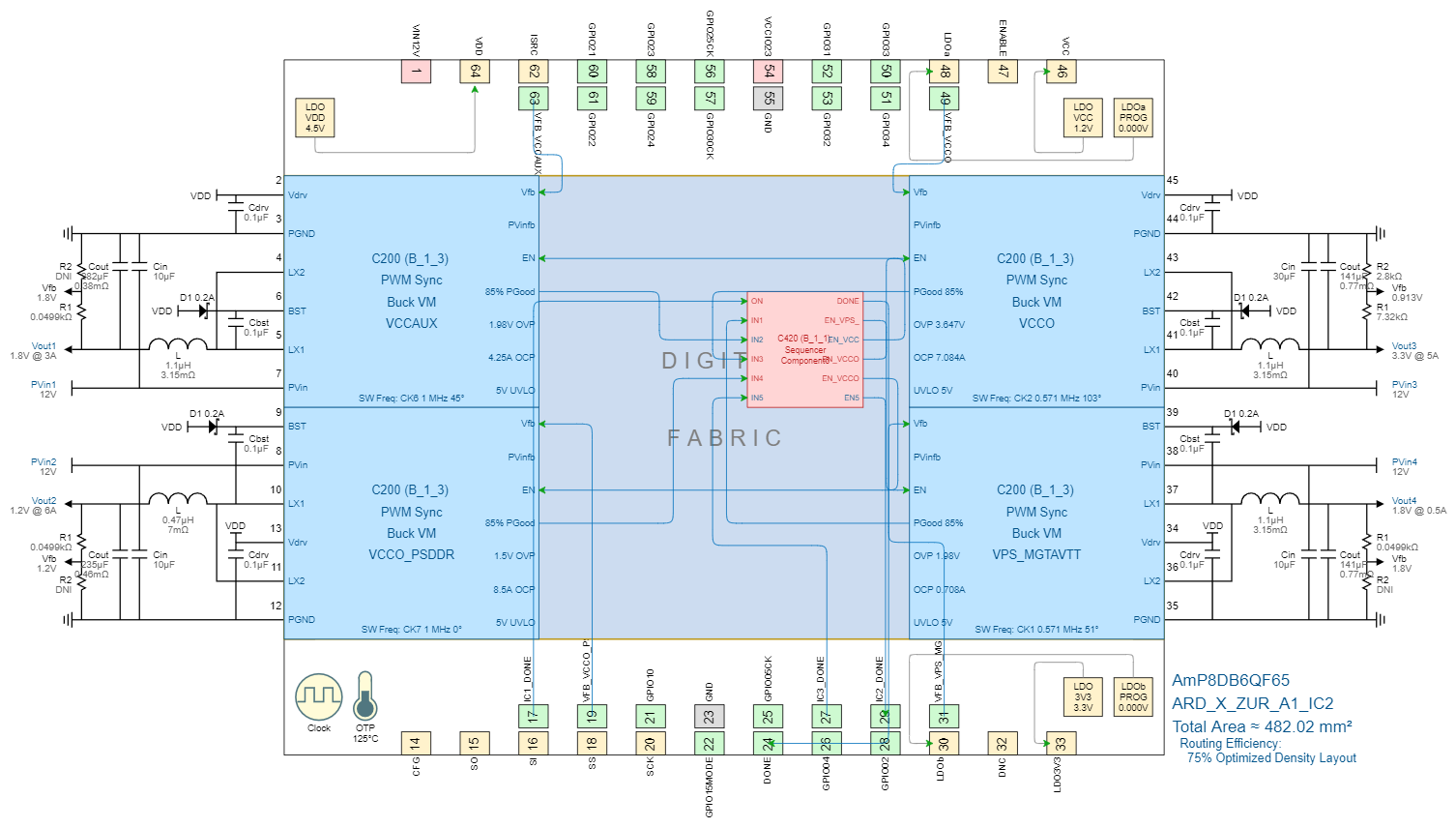

设计视图 IC2

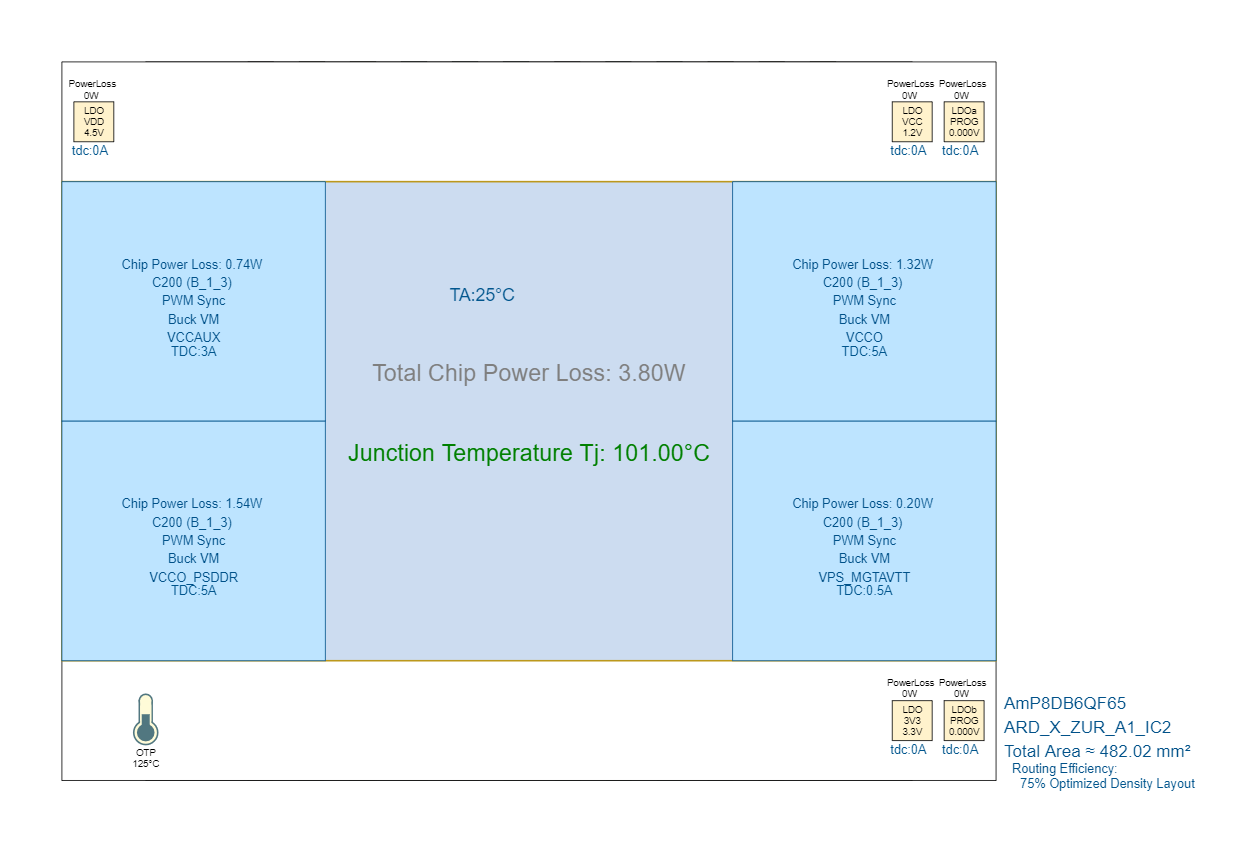

热视图 IC2