Always On, Cost-Optimized (With MGT)

COST-OPTIMIZED WITH MGT

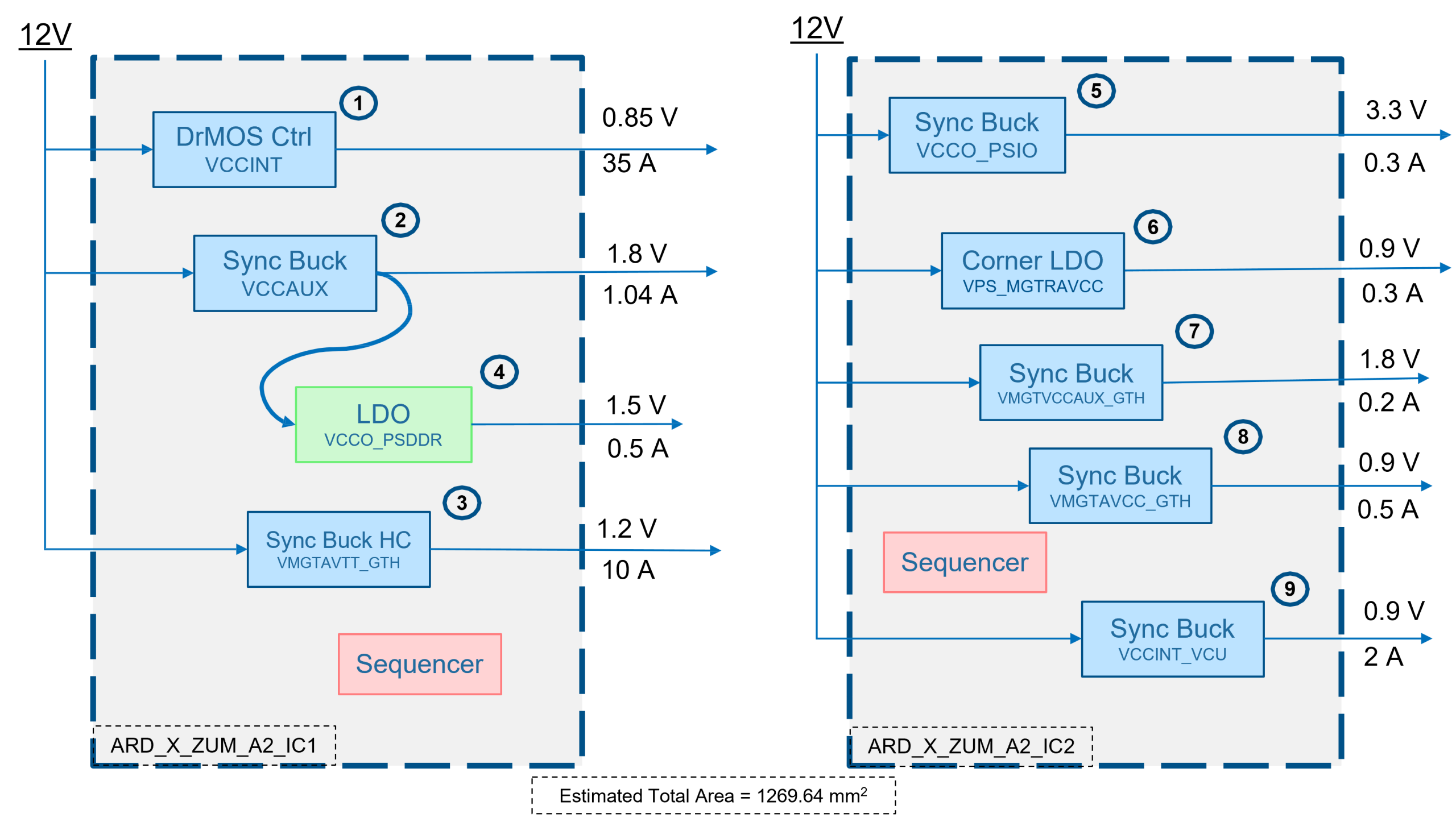

POWER TREE MAPPING – COST-OPTIMIZED WITH MGT

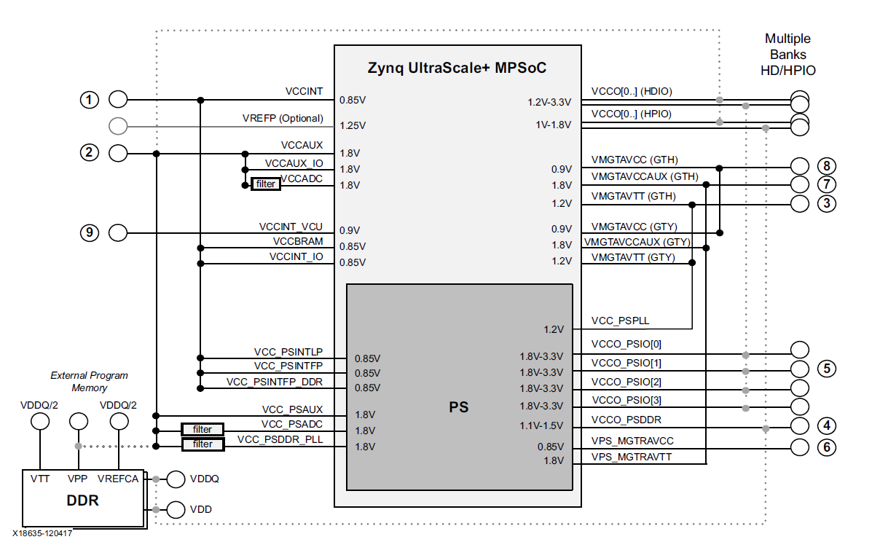

| # | Rail | Seq | Power Component | Type | Upstream Rail | Vinput (V) | Vout (V) | Iout (A) | AnDAPT PMIC |

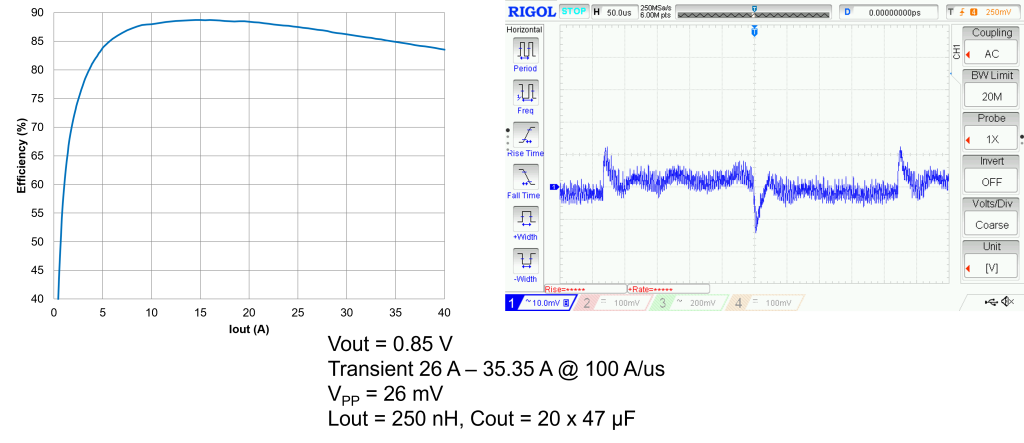

| 1 | VCCINT, VCCBRAM, VCCINT_IO, VCC_PSINTFP, VCC_PSINTLP, VCC_PSINTFP_DDR | 1 | C860 | DrMOS Ctrl | VIN | 12 | 0.85 | 35 | ARD_X_ZUM_A2_IC1 |

| 2 | VCCO_PSDDR | 4 | C710 | SIM LDO | VCCAUX | 1.8 | 1.1 – 1.5 | 0.5 | ARD_X_ZUM_A2_IC1 |

| 3 | VCCAUX, VCCAUX_IO, VCCADC, VCC_PSAUX, VCC_PSADC, VCC_PSDDR_PLL, VCCO_HDIO, VCCO_HPIO | 2 | C200 | Sync Buck | VIN | 12 | 1.8 | 1.04 + 0.5 | ARD_X_ZUM_A2_IC1 |

| 4 | VCCO_PSIO [0:3] | 5 | C200 | Sync Buck | VIN | 12 | 1.8 – 3.3 | 0.300 | ARD_X_ZUM_A2_IC2 |

| 5 | VCCINT_VCU* | 9 | C200 | Sync Buck | VIN | 12 | 0.9 | 2 | ARD_X_ZUM_A2_IC2 |

| 6 | VMGTAVTT (GTH), VMGTYAVTT (GTY), VCC_PSPLL | 3 | C220 | Sync Buck HC | VIN | 12 | 1.2 | 2.6 – 10.6 | ARD_X_ZUM_A2_IC2 |

| 7 | VPS_MGTRAVCC | 6 | CLDO | Corner LDO | VIN | 12 | 0.85/0.9 | 0.3 | ARD_X_ZUM_A2_IC2 |

| 8 | VMGTVCCAUX (GTH), VMGTYVCCAUX (GTH), VPS_MGTRAVTT | 7 | C200 | Sync Buck | VIN | 12 | 1.8 | 0.2 | ARD_X_ZUM_A2_IC2 |

| 9 | VMGTAVCC (GTH), VMGTYAVCC (GTY) | 8 | C200 | Sync Buck | VIN | 1.1 – 1.5 | 0.9 | 0.5 | ARD_X_ZUM_A2_IC2 |

ANDAPT SOLUTION

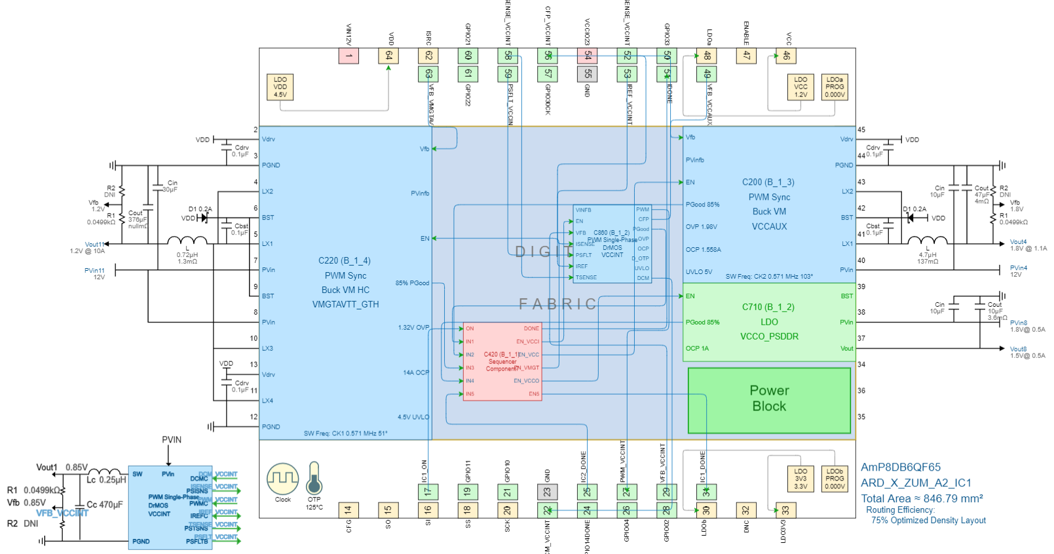

DESIGN VIEW IC1

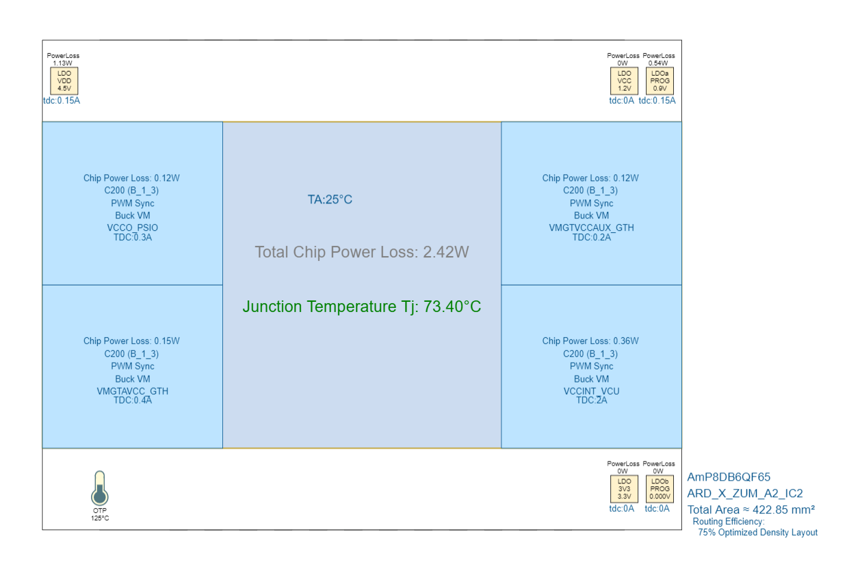

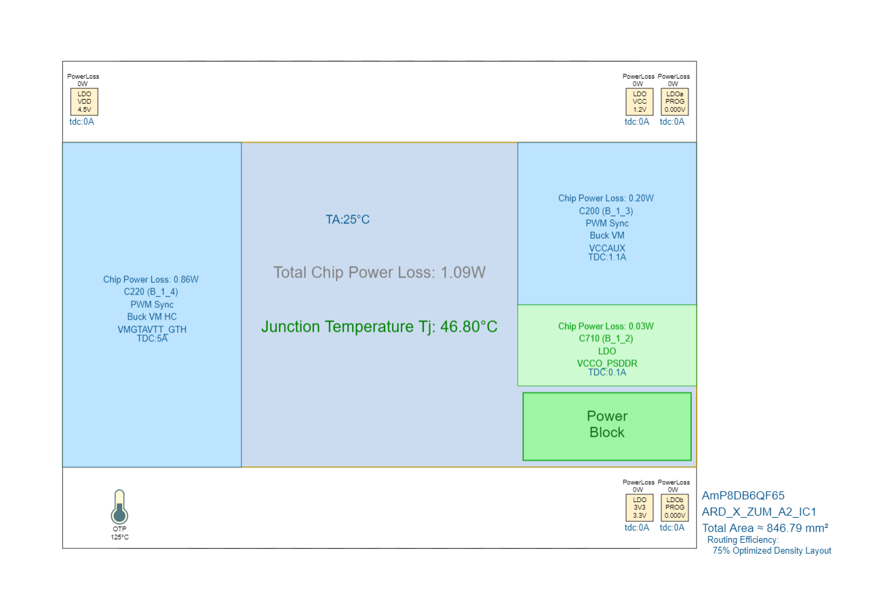

THERMAL VIEW IC1

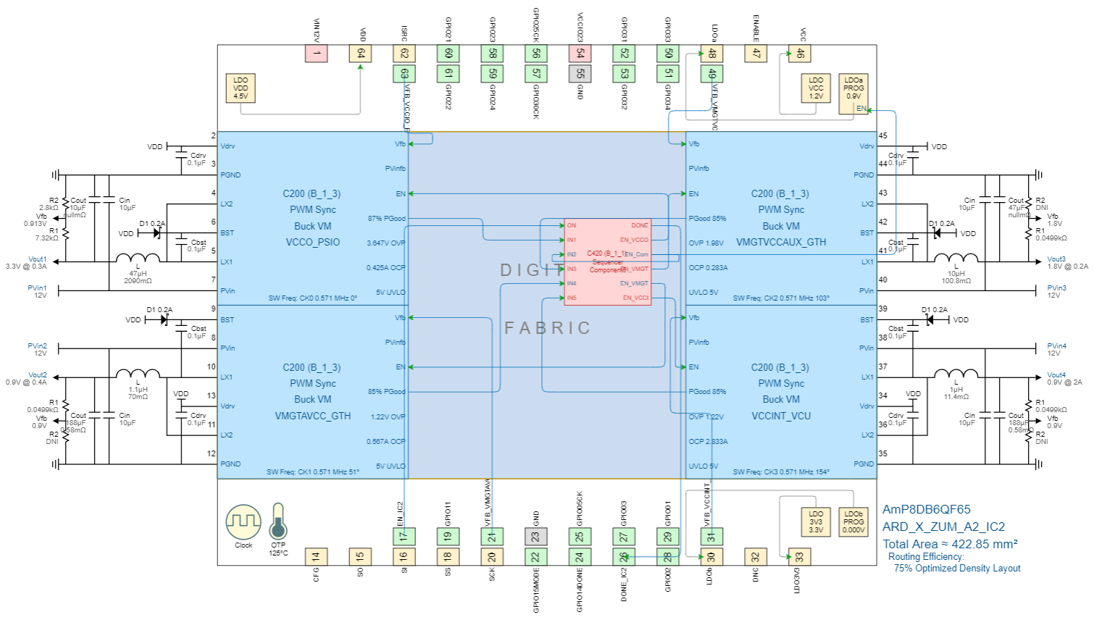

DESIGN VIEW IC2

THERMAL VIEW IC2