Gen 1 Full Power

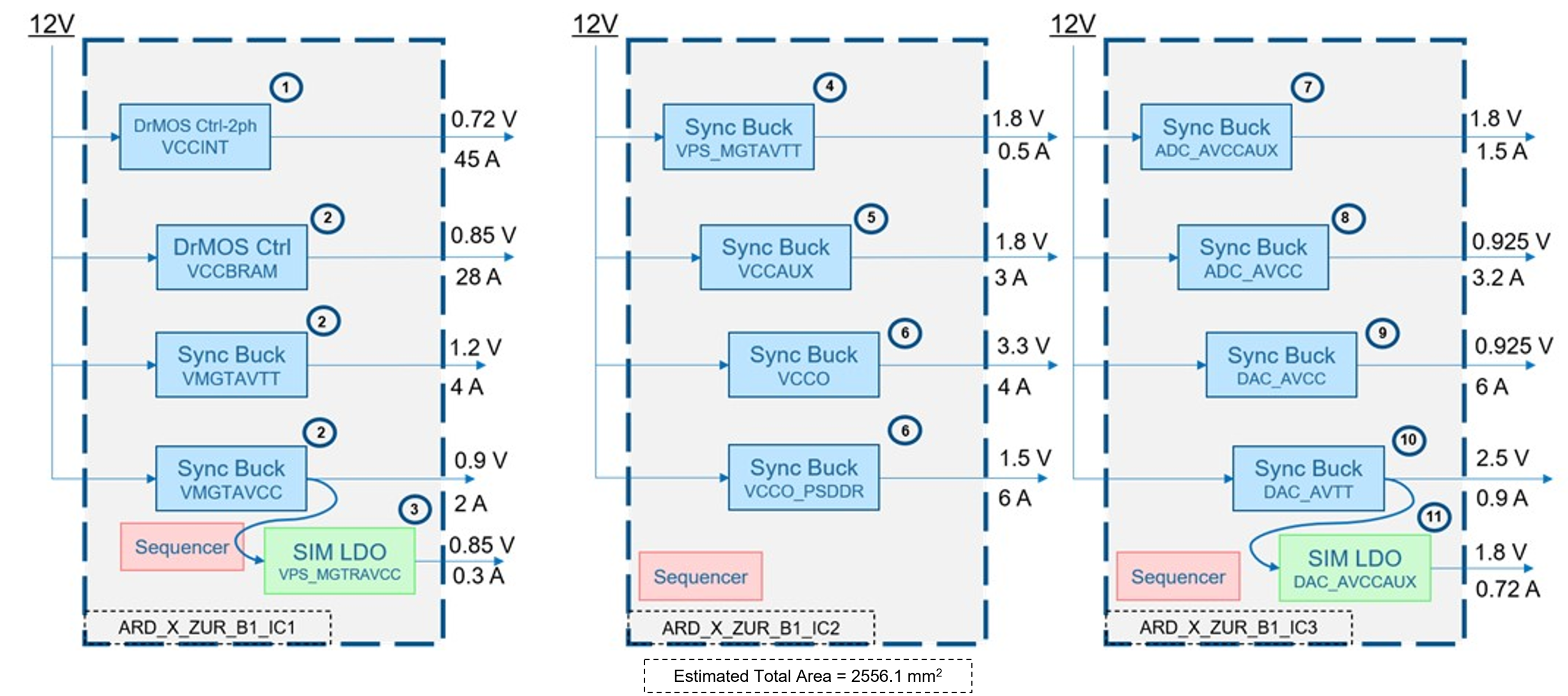

POWER TREE MAPPING – FULL POWER DOMAIN

| # | Rail | Seq | Power Component | Type | Upstream Rail | Vinput (V) | Vout (V) | Iout (A) | AnDAPT PMIC |

| 1 | VCCINT | 1 | C870 | DrMOS Ctrl 2-ph | VIN | 12 | 0.72 / 0.85 | 45 | ARD_X_ZUR_B1_IC1 |

| 2 | VCCBRAM, INT_IO, INT_AMS, SDFEX | 2 | C860 | DrMOS Ctrl 2-ph | VIN | 12 | 0.85 | 28 | ARD_X_ZUR_B1_IC1 |

| 3 | VMGTAVTT, VCC_PSPLL, VCCU_PLL | 2 | C200 | Sync Buck | VIN | 12 | 1.2 | 4 | ARD_X_ZUR_B1_IC1 |

| 4 | MGTAVCC | 2 | C200 | Sync Buck | VIN | 12 | 0.9 | 2 | ARD_X_ZUR_B1_IC1 |

| 5 | VPS_MGTRAVCC | 3 | C710 | SIM LDO | MGTAVCC | 0.9 | 0.85 | 0.3 | ARD_X_ZUR_B1_IC1 |

| 6 | VCCO_PSDDR, DDR_VDDQ | 6 | C200 | Sync Buck | VIN | 12 | 1.1 – 1.5 | 6 | ARD_X_ZUR_B1_IC2 |

| 7 | VCCAUX, ADC, IO, VCCPSAUX, DDR_PLL, ADC | 5 | C200 | Sync Buck | VIN | 12 | 1.8 | 2 – 3 | ARD_X_ZUR_B1_IC2 |

| 8 | VCCO | 6 | C200 | Sync Buck | VIN | 12 | 3.3 / 5 | 4 | ARD_X_ZUR_B1_IC2 |

| 9 | VPS_MGTAVTT, VMGTVAUX | 4 | C200 | Sync Buck | VIN | 12 | 1.8 | 0.5 | ARD_X_ZUR_B1_IC2 |

| 10 | ADC_AVCC | 8 | C200 | Sync Buck | VIN | 12 | 0.925/0.98 | 3.2 | ARD_X_ZUR_B1_IC3 |

| 11 | DAC_AVCC | 9 | C200 | Sync Buck | VIN | 12 | 0.925 | 6 | ARD_X_ZUR_B1_IC3 |

| 12 | ADC_AVCCAUX | 7 | C150 | Async Buck | VIN | 12 | 1.8 | 1.5 | ARD_X_ZUR_B1_IC3 |

| 13 | DAC_AVCCAUX | 11 | C710 | SIM LDO | DAC_AVTT | 2.5 | 1.8 | 0.72 | ARD_X_ZUR_B1_IC3 |

| 14 | DAC_AVTT | 10 | C200 | Sync Buck | VIN | 12 | 2.5 / 3.3 | 0.9 | ARD_X_ZUR_B1_IC3 |

ANDAPT SOLUTION – FULL POWER DOMAIN

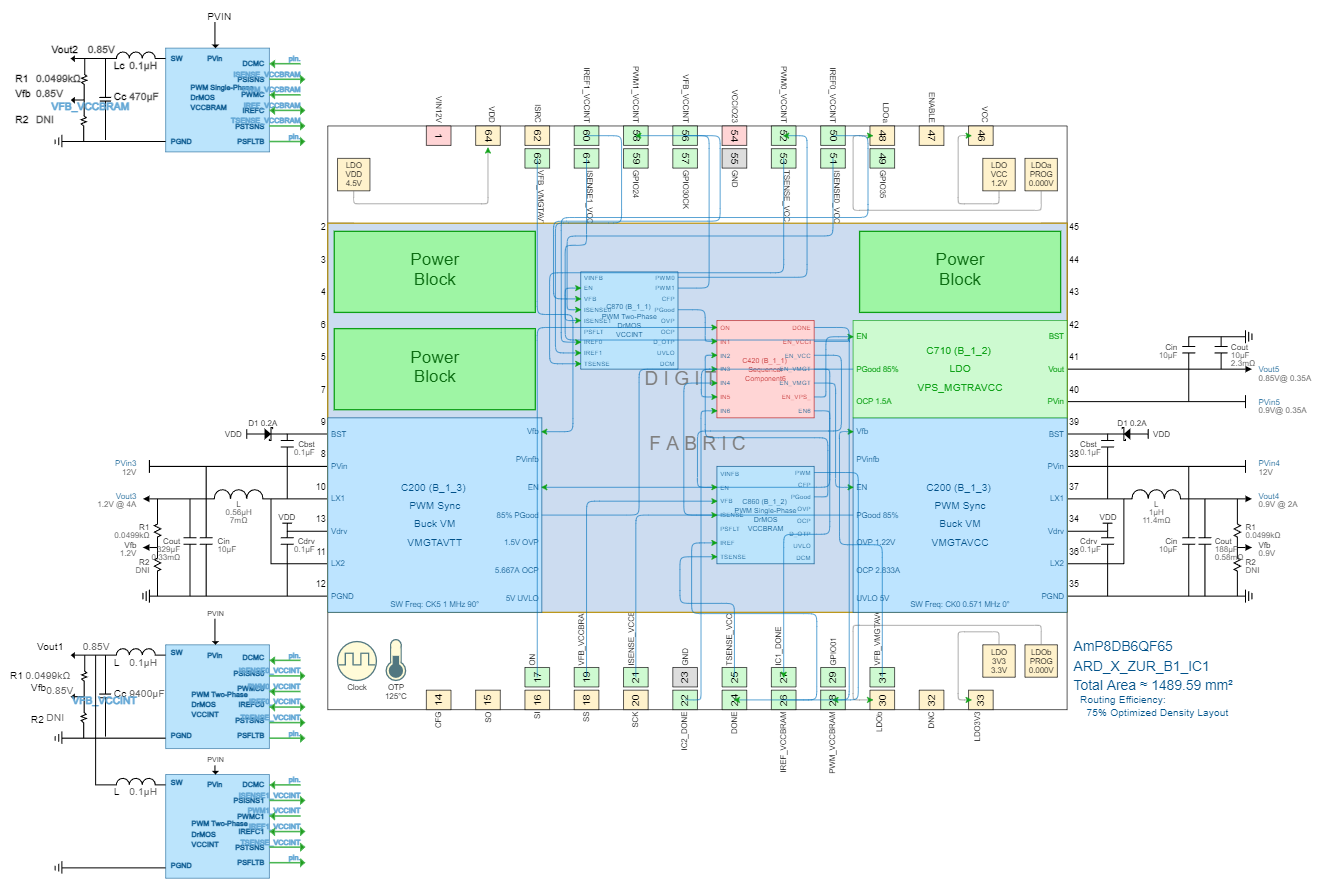

DESIGN VIEW IC1 – MANDATORY

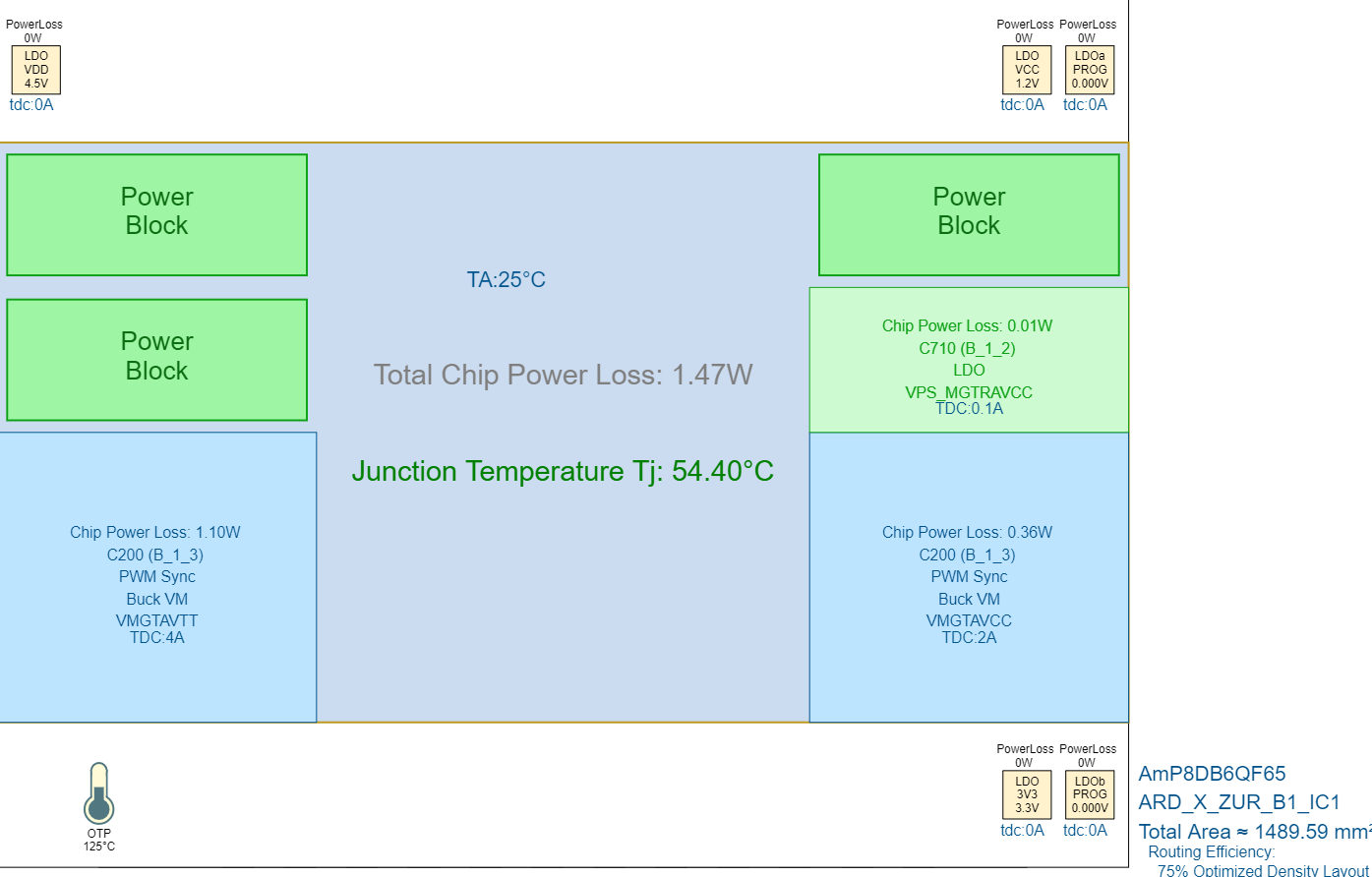

THERMAL VIEW IC1 – MANDATORY

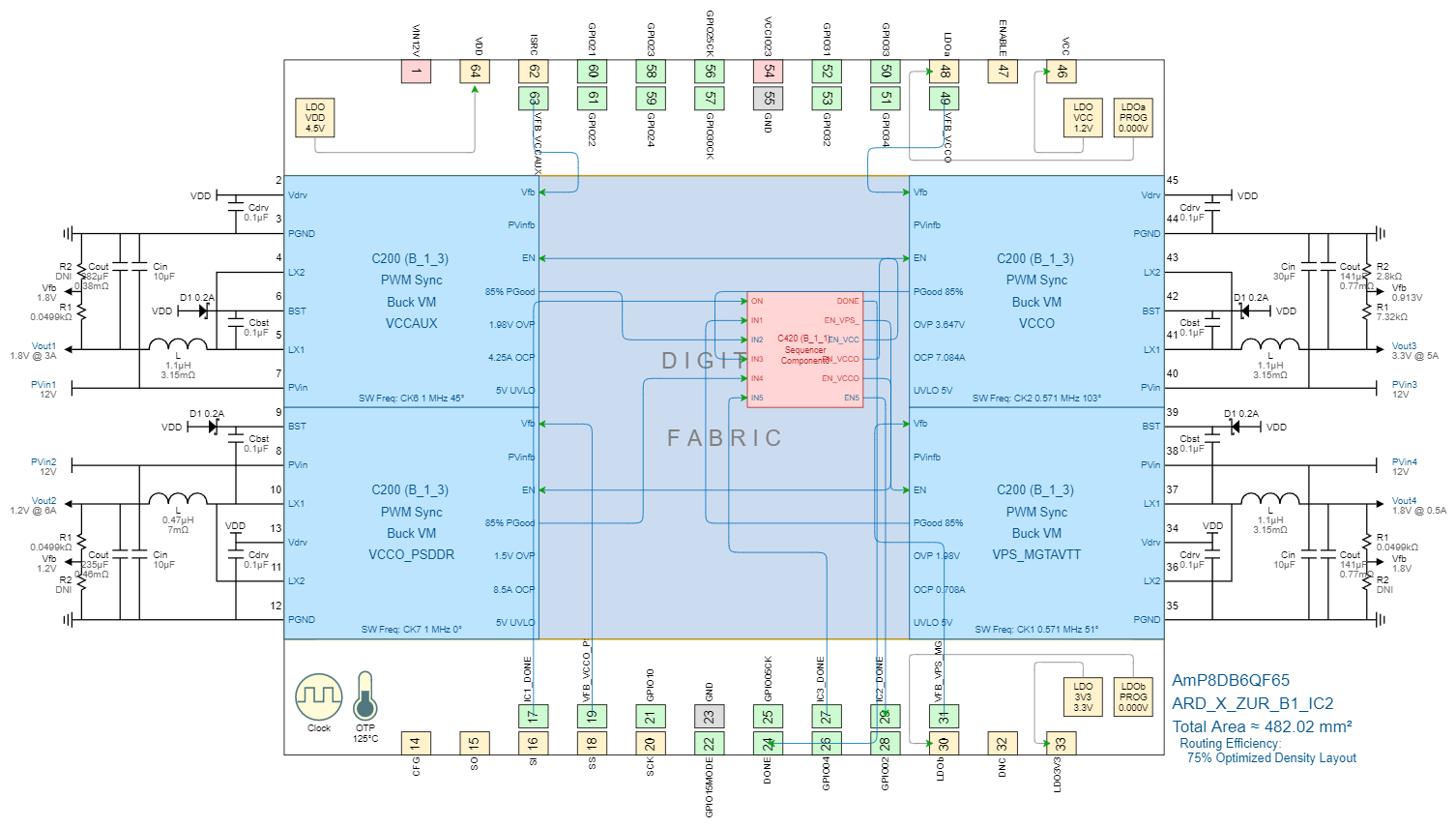

DESIGN VIEW IC2 – MANDATORY

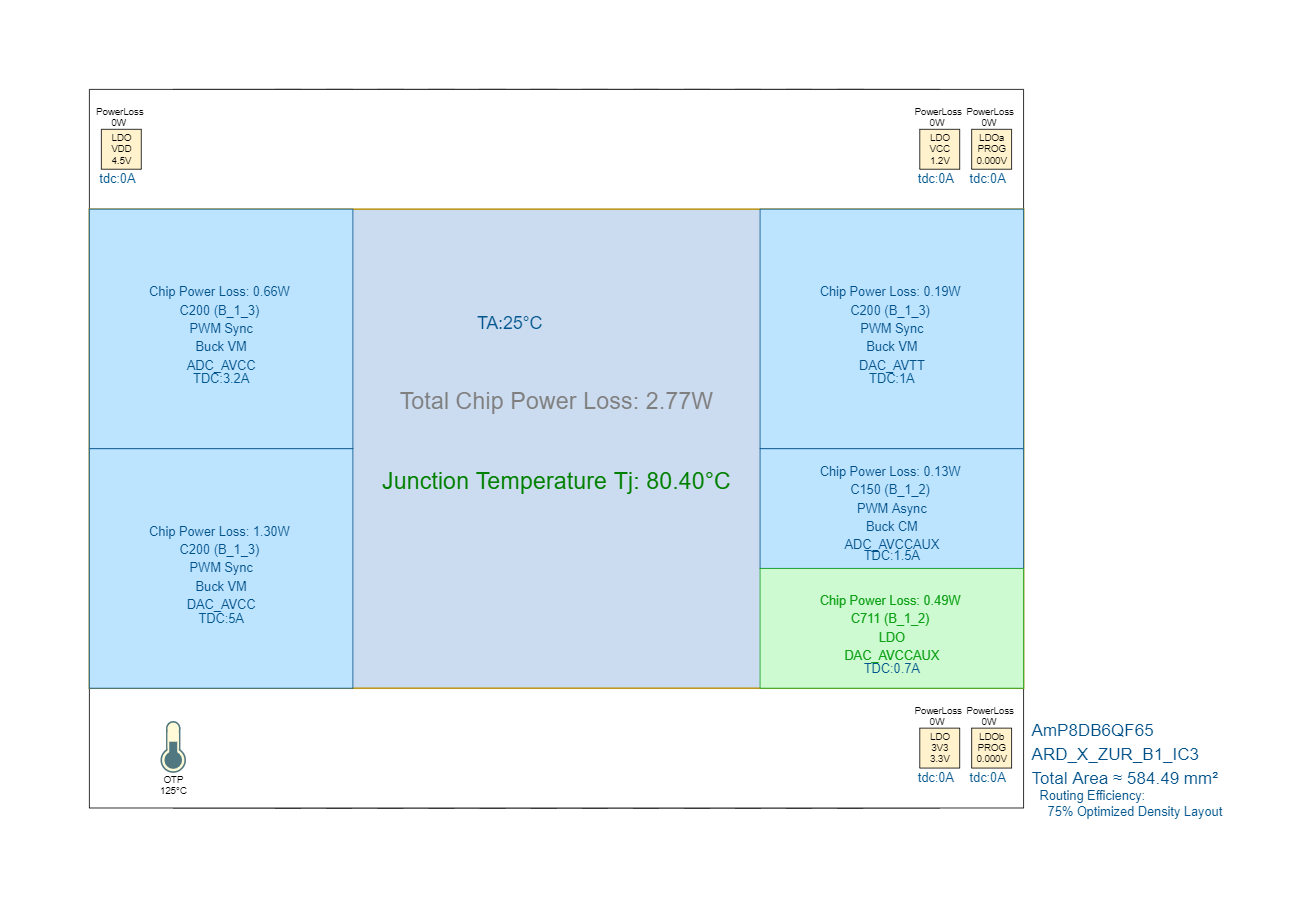

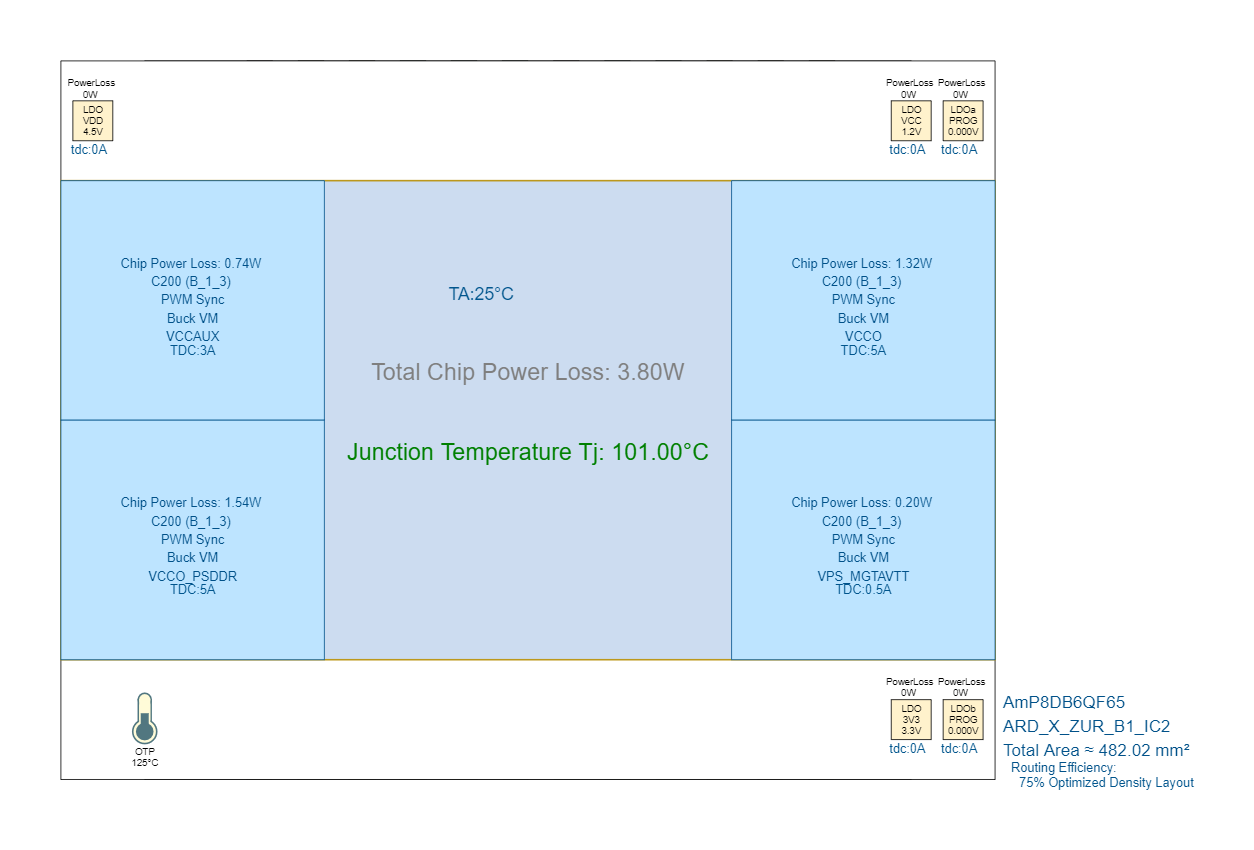

THERMAL VIEW IC2 – MANDATORY

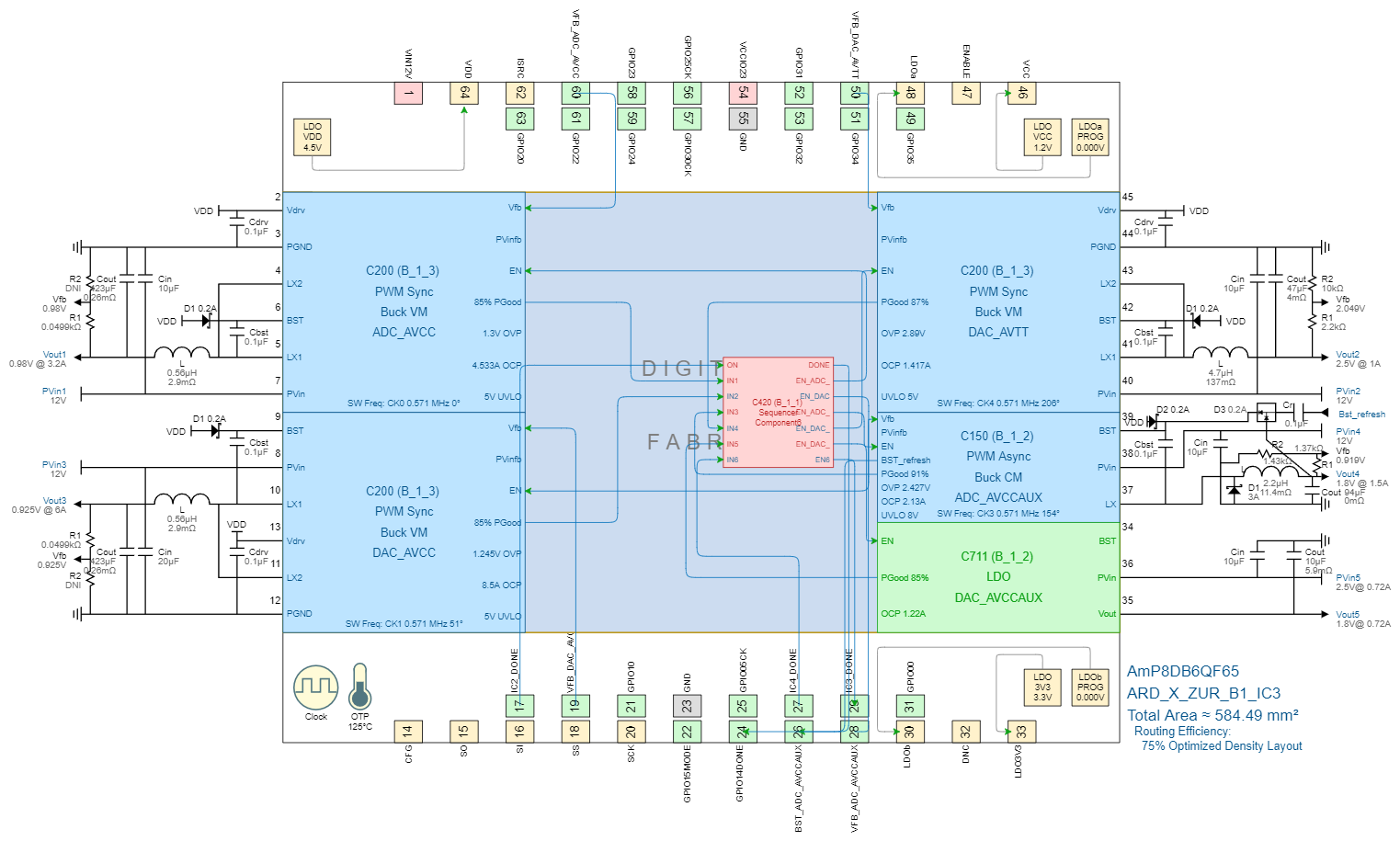

DESIGN VIEW IC3 – OPTIONAL

THERMAL VIEW IC3 – OPTIONAL